### iSBC® 028CX/056CX/012CX/010CX/020CX (CX-SERIES) RAM BOARDS HARDWARE REFERENCE MANUAL

Order Number: 145158-003

### iSBC® 028CX/056CX/012CX/010CX/020CX (CX-SERIES) RAM BOARDS HARDWARE REFERENCE MANUAL

Order Number: 145158-003

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instruction manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A Computing Device pursuant to Subpart J of Part 15 of FCC rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a) (9).

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Intel Corporation.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

| BITBUS             | iLBX                   | iPDS            | Plug-A-Bubble |

|--------------------|------------------------|-----------------|---------------|

| COMMputer          | im                     | iRMX            | PROMPT        |

| CREDIT             | iMMX                   | iSBC            | Promware      |

| Data Pipeline      | Insite                 | iSBX            | QUEX          |

| GENIUS             | Intel                  | iSDM            | QUEST         |

| Ą                  | intel                  | iSXM            | Ripplemode    |

| 1                  | intelBOS               | Library Manager | RMX/80        |

| I <sup>2</sup> ICE | Intelevision           | MCS             | RUPI          |

| ICE                | inteligent Identifier  | Megachassis     | Seamless      |

| iCS                | inteligent Programming | MICROMAINFRAME  | SOLO          |

| iDBP               | Intellec               | MULTIBUS        | SYSTEM 2000   |

| iDIS               | Intellink              | MULTICHANNEL    | UPI           |

| 1013               | iOSP                   | MULTIMODULE     |               |

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

Copyright @ 1984, Intel Corporation

<sup>\*</sup>MULTIBUS is a patented Intel bus.

| REV. | REVISION HISTORY                                  | DATE |

|------|---------------------------------------------------|------|

| -001 | Original Issue                                    | 9/82 |

| -002 | Change Notice (146094-001). Board design changes. | 6/83 |

|      |                                                   |      |

|      |                                                   |      |

|      |                                                   |      |

|      |                                                   |      |

|  | , |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

#### **PREFACE**

This manual describes the five "CX-Series" Random Access Memory (RAM) memory boards: the iSBC Ø28CX board, the iSBC Ø56CX board, the iSBC Ø12CX board, the iSBC Ø19CX board, and the iSBC Ø2ØCX RAM board. The boards differ only in RAM capacity. Each board features error checking and correcting (ECC) circuitry, MULTIBUS compatibility, and iLBX bus compatibility. This manual explains how to use the boards features in a typical installation. For additional information, the following publications are available from the Intel Literature Department:

• Intel MULTIBUS® Specification, Order Number: 98ØØ683

• Intel iLBX<sup>™</sup> Bus Specification, Order Number: 145695

Intel Microsystems Component Handbook (2 Vol.)

Order Number: 23Ø843

#### **NOTES**

Throughout this manual, a slash (/) following a signal name means that the signal is active—low.

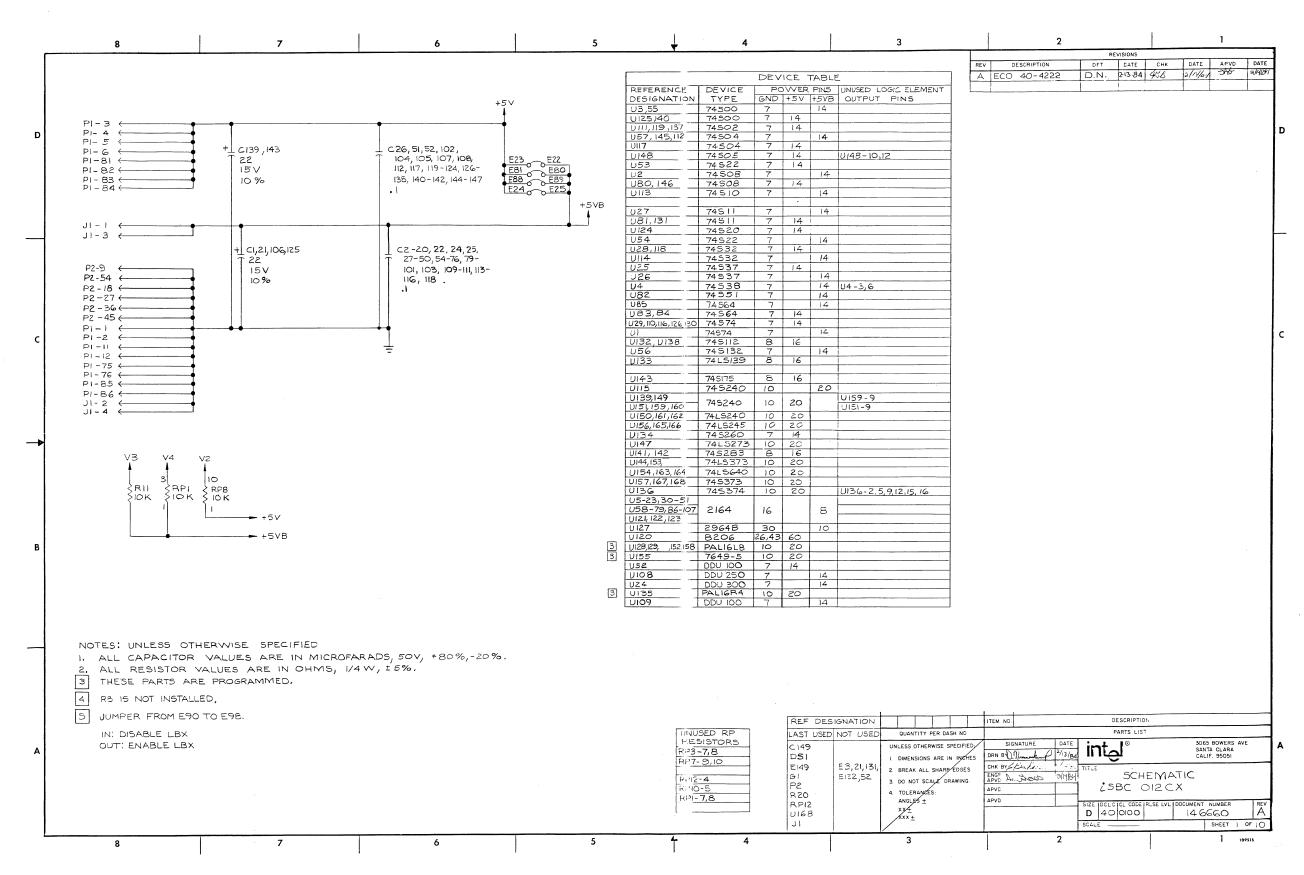

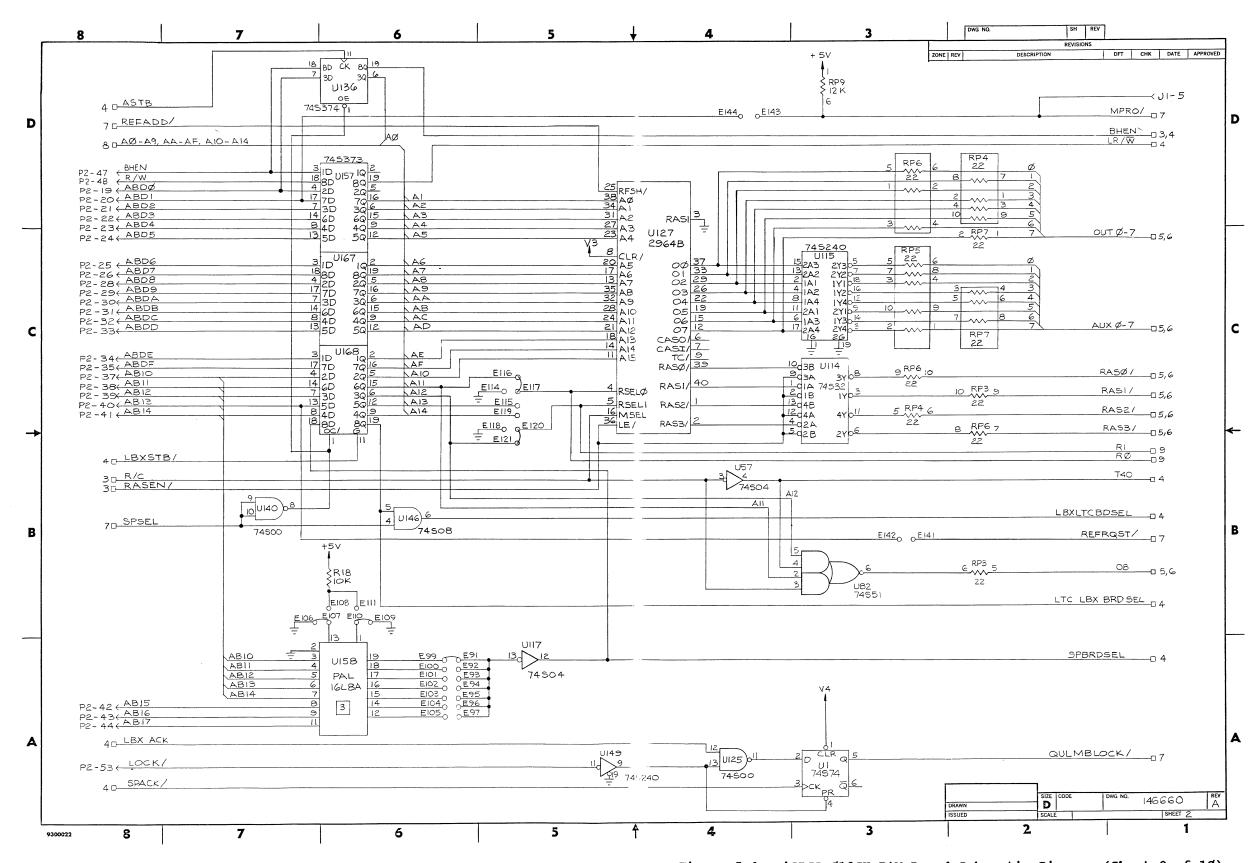

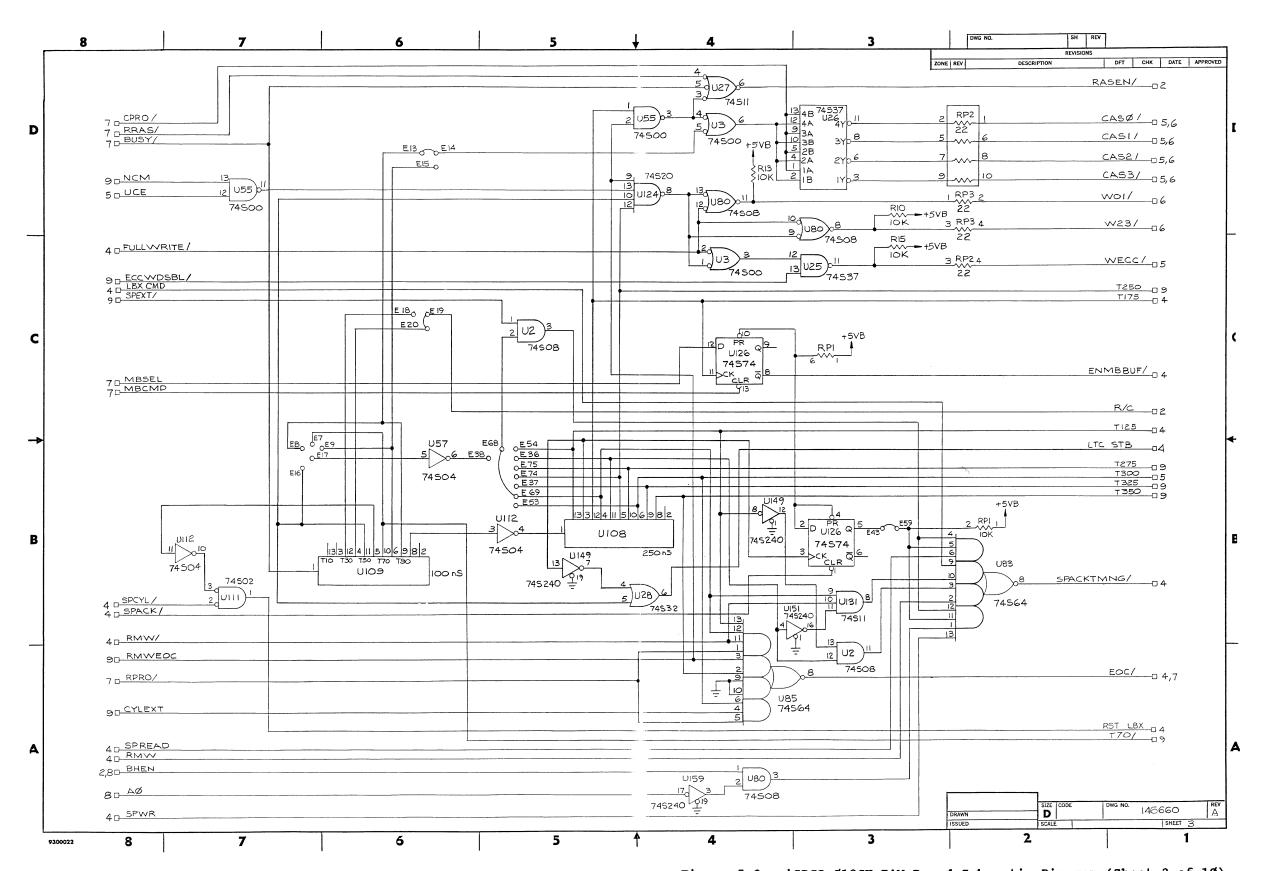

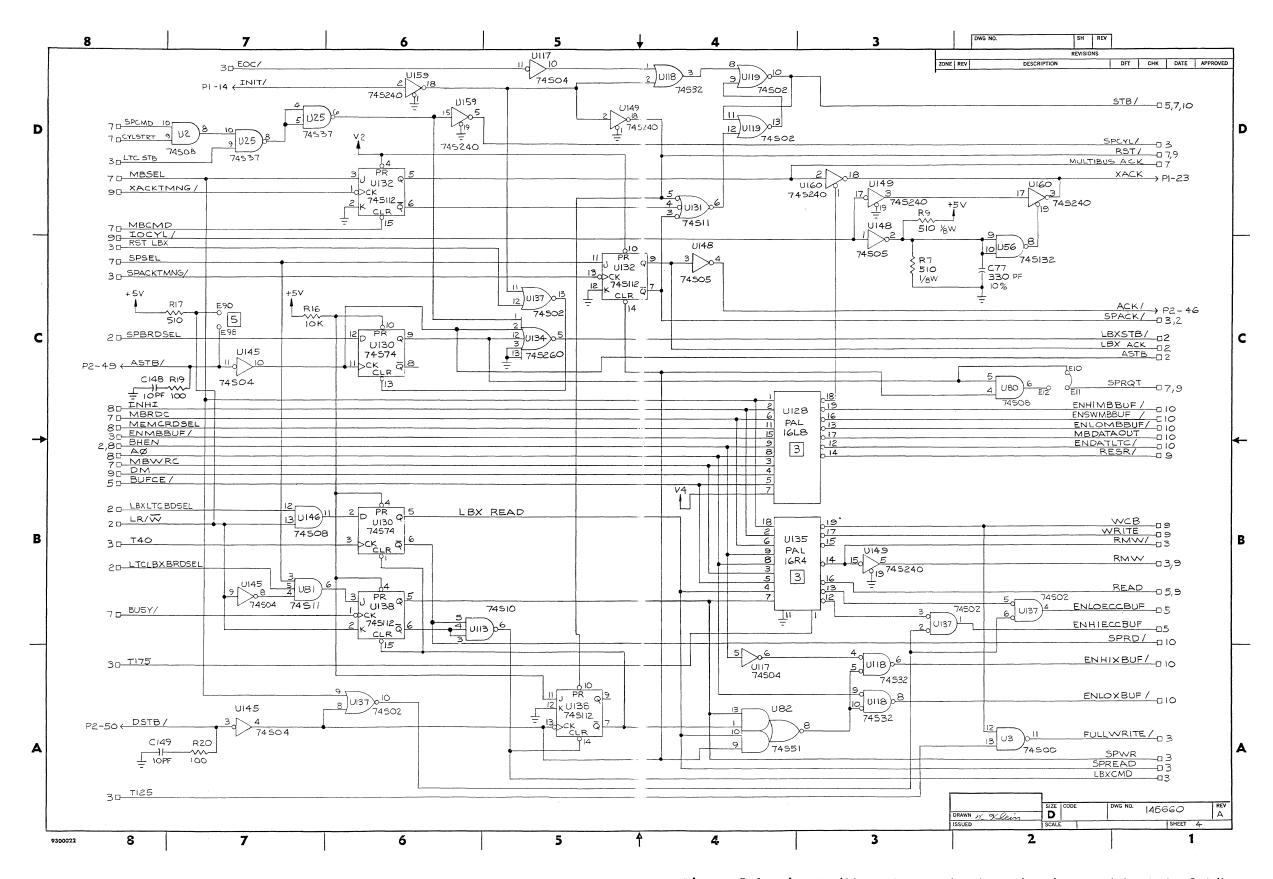

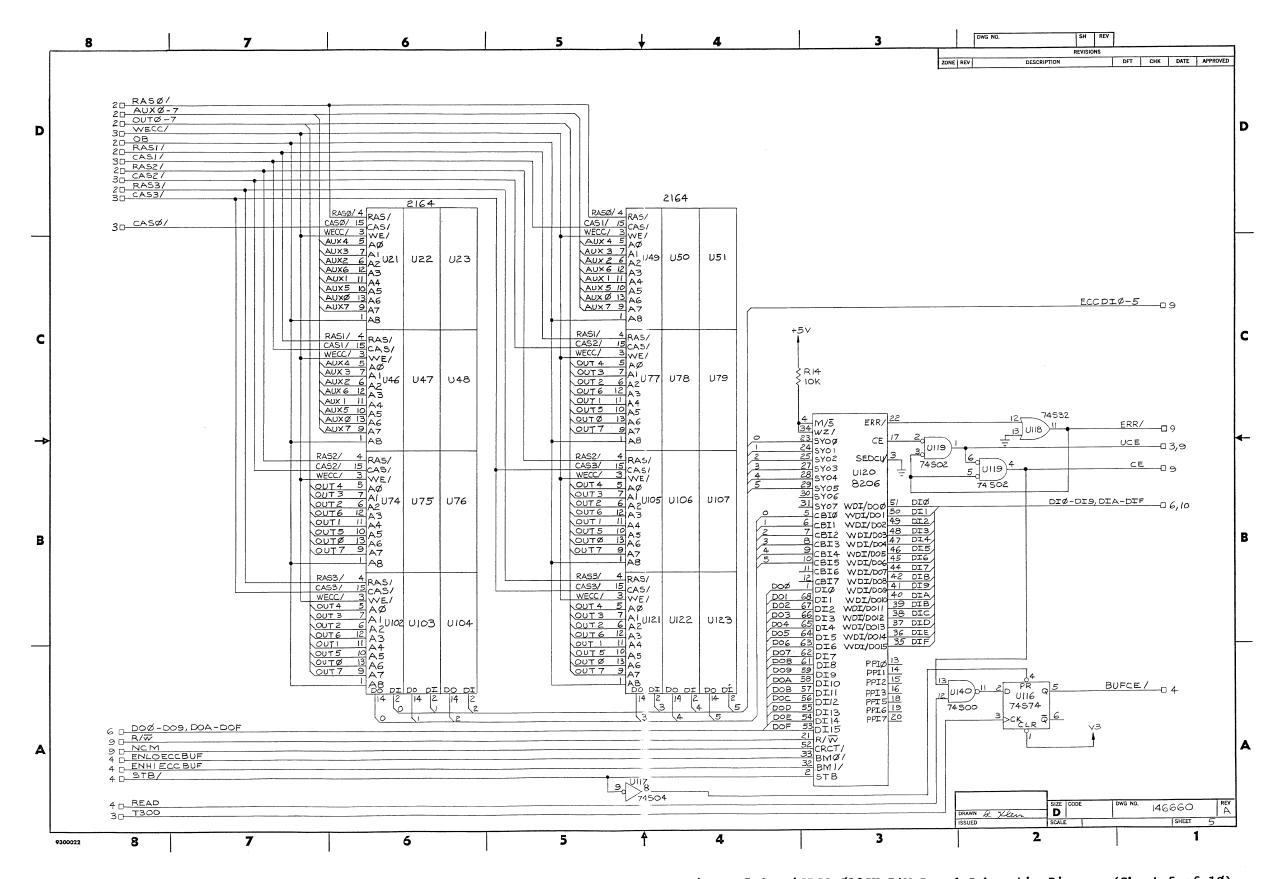

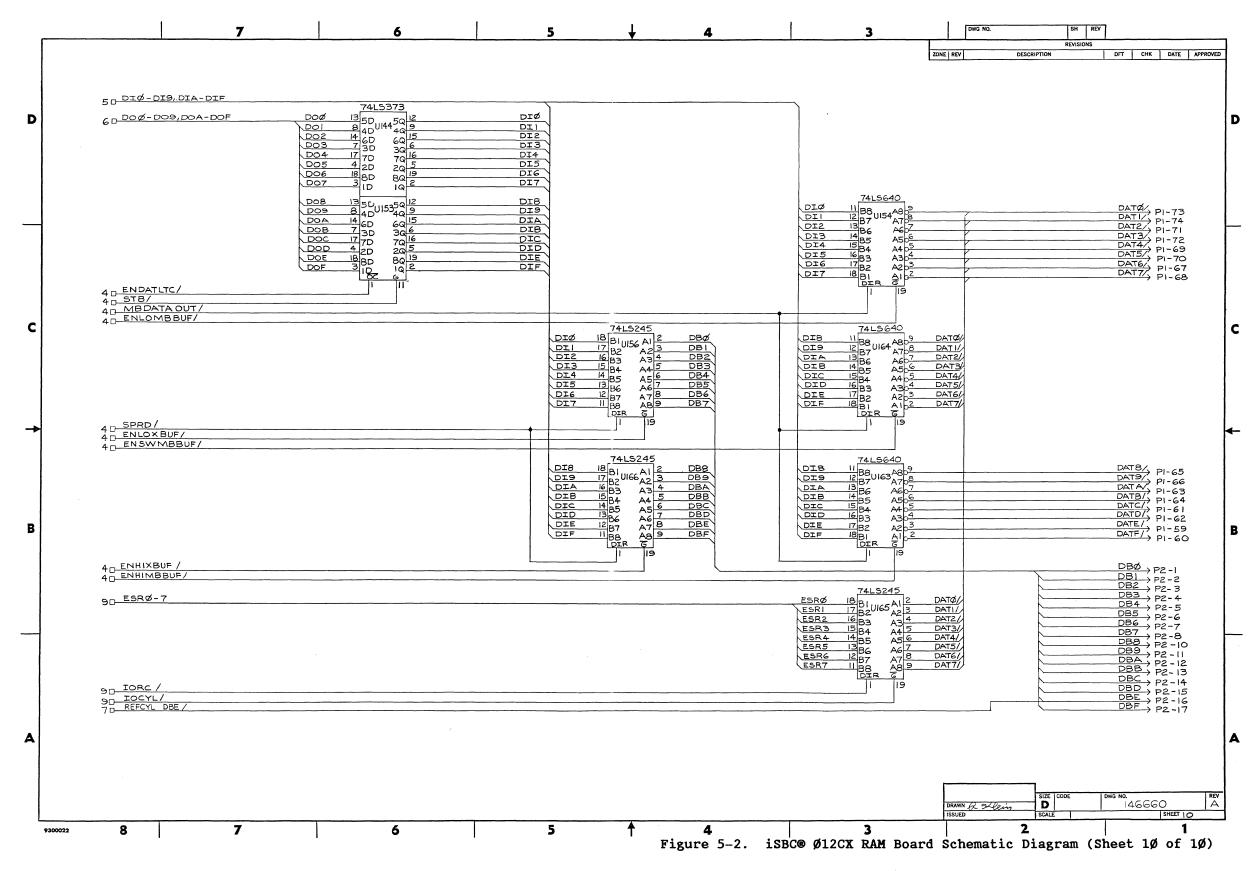

Each RAM board is shipped with a matching set of schematic diagrams. These diagrams should be kept for future reference. The schematic diagrams used in Chapter 5 are for the iSBC 012CX RAM board and are used to represent the iSBC 028CX/056CX/012CX/010CX/020CX RAM Boards. For current and individual board schematics, refer to the set of schematic diagrams shipped with each board.

# **Lintel**

### **CONTENTS**

|                                                                      | PAGE |

|----------------------------------------------------------------------|------|

| CHAPTER 1                                                            |      |

| GENERAL INFORMATION                                                  |      |

| 1.1 Introduction                                                     | 1-1  |

| 1.2 Description                                                      | 1-2  |

| 1.3 Documentation Supplied                                           | 1-3  |

| 1.4 Specifications                                                   | 1-3  |

| 1.5 Compliance Level: 796 Bus Specification (IEEE Standard)          | 1-5  |

| 1.6 iLBX™ Bus Compliance Level                                       | 1-6  |

|                                                                      |      |

| CHAPTER 2                                                            |      |

| PREPARATION FOR USE                                                  |      |

| 2.1 Introduction                                                     | 2-1  |

| 2.2 Unpacking and Inspection                                         | 2-1  |

| 2.3 Installation Considerations                                      | 2-1  |

| 2.3.1 Power Requirements                                             | 2-1  |

| 2.3.2 Cooling Requirements                                           | 2-1  |

| 2.3.3 MULTIBUS® Interfacing Requirements                             | 2-2  |

| 2.4 Jumper Configurations                                            | 2-2  |

| 2.4.1 MULTIBUS® Memory Addressing                                    | 2-2  |

| 2.4.1.1 MULTIBUS® Page Address Selection Jumpers                     | 2-3  |

| 2.4.1.2 MULTIBUS® Base Address Jumpers                               | 2-4  |

| 2.4.1.3 iLBX <sup>TM</sup> Bus Memory Addressing                     | 2-8  |

| 2.4.1.4 iLBX <sup>™</sup> Bus Base Address and Address Range Jumpers | 2-8  |

| 2.4.1.5 Memory De-select (iSBC@ Ø12CX/Ø1ØCX/Ø2ØCX RAM Boards Only)   | 2-14 |

| 2.4.2 ECC I/O Address Selection                                      | 2-15 |

| 2.4.3 iLBX <sup>TM</sup> Bus Interface Address Strobe Jumper         | 2-17 |

| 2.4.4 iLBX <sup>TM</sup> Bus Speed Selection Jumper                  | 2-17 |

| 2.4.5 Interrupt Level Selection Jumpers                              | 2-17 |

| 2.4.6 External Refresh (REFRQST) Jumper                              | 2-18 |

| 2.4.7 iLBX <sup>TM</sup> Bus Acknowledge Time Selection Jumpers      | 2-18 |

| 2.4.8 Battery Back-Up and Memory Save Jumpers                        | 2-20 |

| 2.5 Board Installation                                               | 2-21 |

| 2.6 Factory Default Jumpers                                          | 2–21 |

|                                                                      |      |

| CHAPTER 3                                                            |      |

| ECC OPERATION AND PROGRAMMING INFORMATION                            |      |

| 3.1 Introduction                                                     | 3-1  |

| 3.2 Modes of ECC Operation                                           | 3-1  |

| 3.2.1 Interrupt on Any Error Mode                                    | 3-1  |

| 3.2.2 Interrupt on Non-Correctable Error Only Mode                   | 3-1  |

| 3.2.3 Correcting Mode                                                | 3–2  |

| 3.2.4 Non-Correcting Mode                                            | 3–2  |

| 3.2.5 Diagnostic Mode                                                | 3-2  |

| 3.2.6 Examine Syndrome Word Mode                                     | 3-2  |

| 3.3 Programming Information                                          | 3-2  |

| 3.3.1 Control Status Register (CSR) Programming                      | 3-3  |

| 3.3.2 Interrupt on Any Error Mode Programming                        | 3-5  |

## CONTENTS (continued)

|                                                                         | PAGE  |

|-------------------------------------------------------------------------|-------|

| CHAPTER 3 (continued)                                                   |       |

| 3.3.3 Interrupt on Non-Correctable Error Only Mode                      |       |

| 3.3.4 Correcting and Non-Correcting Mode Programming                    |       |

| 3.3.5 Diagnostic Mode Programming                                       |       |

| 3.4 Error Status Register (ESR)                                         |       |

| 3.5 Software Initialization Procedure                                   |       |

|                                                                         |       |

| CHAPTER 4                                                               |       |

| MEMORY BOARD OPERATION                                                  |       |

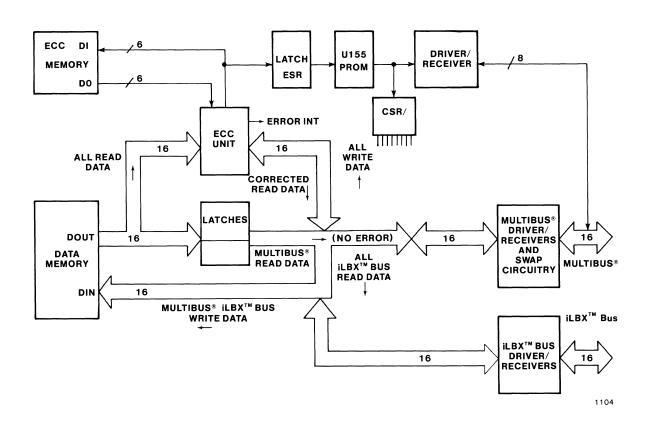

| 4.1 Introduction                                                        |       |

| 4.2 Memory Operations                                                   |       |

| 4.3 Error Checking and Correction (ECC) Operation                       |       |

| 4.3.1 MULTIBUS® ECC Operation                                           |       |

| 4.3.3 Diagnostic Mode                                                   |       |

| 4.4 MULTIBUS® LOCK/ and iLBX™ Bus LOCK/ Signals                         |       |

|                                                                         |       |

| CHAPTER 5                                                               |       |

| SERVICE INFORMATION                                                     |       |

| 5.1 Introduction                                                        | 5–1   |

| 5.2 Service and Repair Assistance                                       |       |

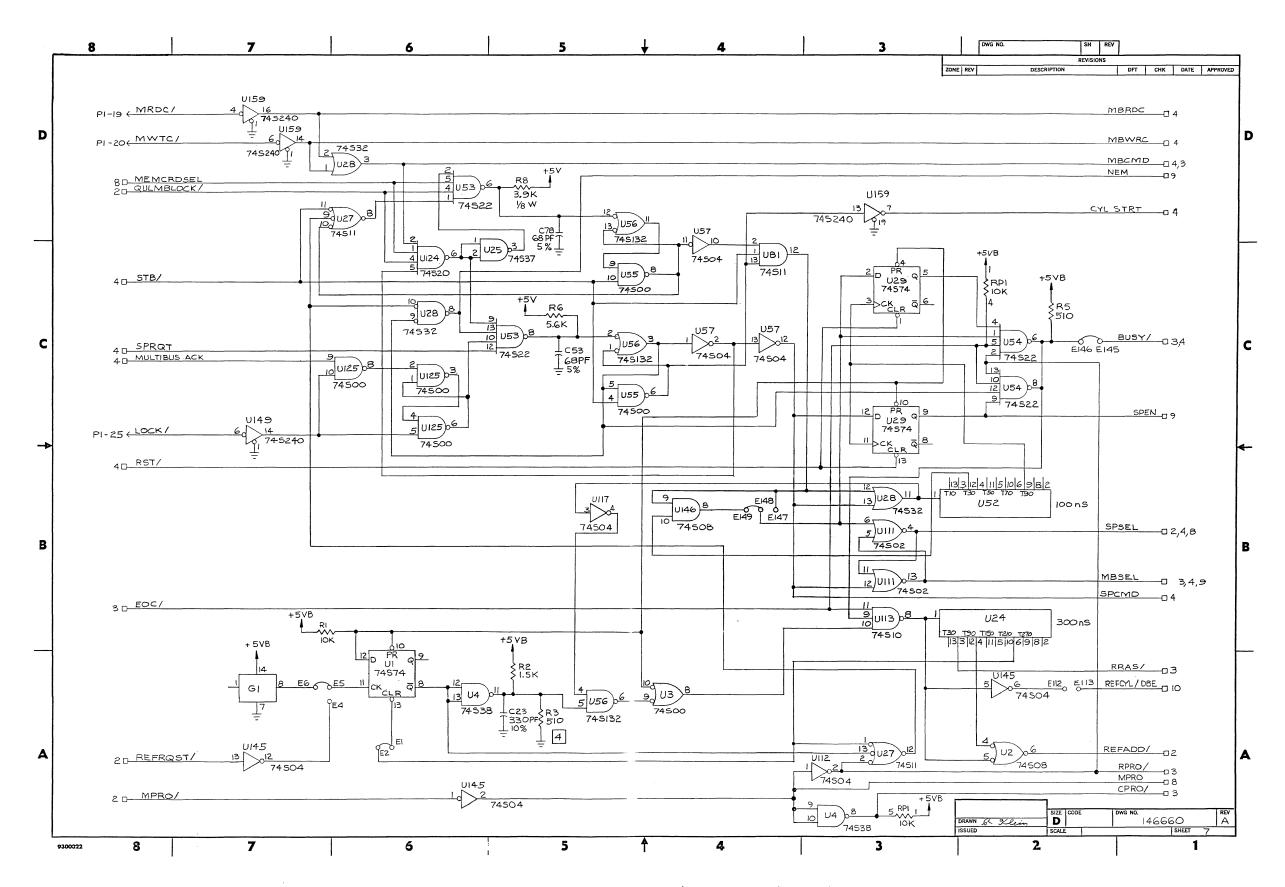

| 5.3 Schematic Diagrams                                                  | 5–2   |

|                                                                         |       |

| APPENDIX A CONNECTOR PIN ASSIGNMENTS                                    |       |

| CONNECTOR PIN ASSIGNMENTS                                               | A-1   |

| APPENDIX B                                                              |       |

| PAL PROGRAMMING                                                         |       |

| B.1 Introduction                                                        | . B-1 |

| B.2 iLBXTM Base Address PAL (U158)                                      |       |

| B.3 ECC Control Port Address PAL (U152)                                 | . B-1 |

|                                                                         |       |

| TABLES                                                                  |       |

| 1-1. Memory and ECC Devices (64K-bit)                                   | 3.0   |

| 1-1. Memory and ECC Devices (64K-bit)                                   |       |

| 2-1. Heat Dissipation                                                   |       |

| 2-2. MULTIBUS® Page Select Jumpers                                      |       |

| 2-3. MULTIBUS® Base Address Selection Jumpers                           |       |

| 2-4. iLBX <sup>TM</sup> Bus Address Range Jumpers for iSBC® Ø28CX Board |       |

| 2-5. iLBX <sup>TM</sup> Bus Address Range Jumpers for iSBC® Ø56CX Board | 2-1Ø  |

# TABLES (continued)

|                |                                                          | PAGE       |

|----------------|----------------------------------------------------------|------------|

| 2-6.           | il DVIN Dug Addmagg Dange Tumpang Com iGDCO di 20V Dangd | 0 11       |

| 2-6.<br>2-7.   | iLBXT Bus Address Range Jumpers for iSBC® Ø12CX Board    | 2-11       |

| 2-7.<br>2-8.   | iLBX™ Bus Address Range Jumpers for iSBC® Ø1ØCX Board    | 2-12       |

| 2-8.<br>2-9.   | iLBXT Bus Address Range Jumpers for iSBC® Ø2ØCX Board    | 2-13       |

| 2-9.           | MULTIBUS® Address Range Selection Jumpers                | 2-15       |

| 2-1Ø.          | with Deselect Option (Jumper 33-34)                      | 2-13       |

| 2-10.<br>2-11. | I/O Address Jumpers                                      | 2-18       |

| 2-11.          | Interrupt Level Selection Jumpers                        | 2-10       |

| 2-12.          | Factory Installed Jumpers                                | 2-29       |

| 2-13.<br>3-1.  | RAM Board Control Status Register Format Summary         | 3-4        |

| 3-1.           | Typical ECC Operating Modes (Hex)                        | 3-5        |

| 3-2.           | RAM Board Error Status Register Format                   | 3-6        |

| 3-3.<br>A-1.   | MULTIBUS® Connector P1 Pin Assignments                   | 3-0        |

| H-1.           | for iSBC@ CX-Series RAM Boards                           | A-1        |

| A-2.           | iLBX™ Bus Connector P2 Pin Assignments                   | H-I        |

| H-2.           | for iSBC@ CX-Series RAM Boards                           | A-3        |

| A-3.           | iLBX <sup>TM</sup> Bus Connector J1 Pin Assignments      | H-3        |

| H-3.           | for iSBC@ CX-Series RAM Boards                           | A-4        |

| B-1A.          | U158 PAL Programming for iSBC® Ø28CX Board               | B-2        |

| B-1B.          | U158 PAL Programming for iSBC® Ø56CX Board               | B-2<br>B-3 |

| B-1C.          | U158 PAL Programming for iSBC® Ø12CX Board               | B-3        |

| B-1D.          | U158 PAL Programming for iSBC® Ø1ØCX Board               | B-4<br>B-6 |

| B-1E.          | U158 PAL Programming for iSBC® Ø2ØCX Board               | B-7        |

| B-2.           | U152 PAL Programming                                     | B-8        |

| D-2.           | OIDZ TRE TEOGRAMMING                                     | D-0        |

|                |                                                          |            |

|                | FIGURES                                                  |            |

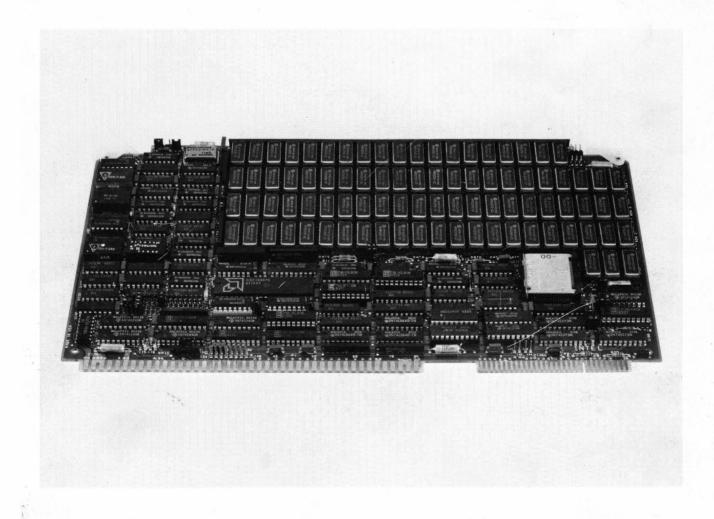

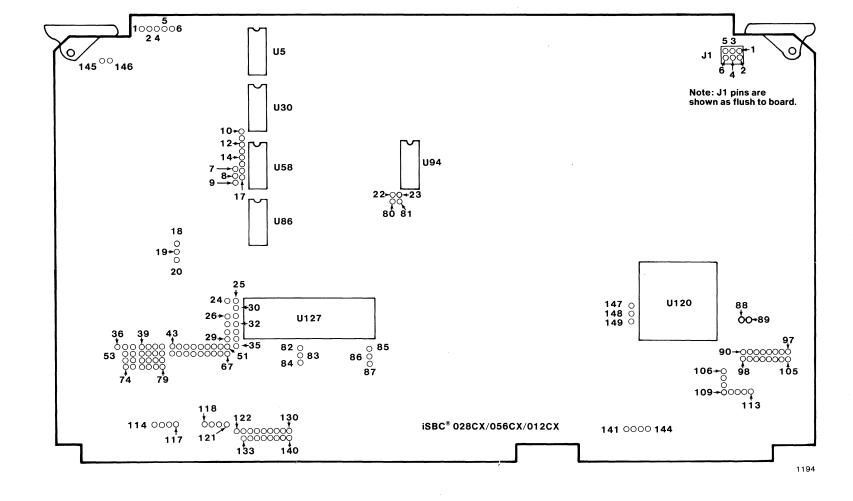

| 1-1.           | iSBC@ Ø12CX Random Access Memory Board                   | 1–1        |

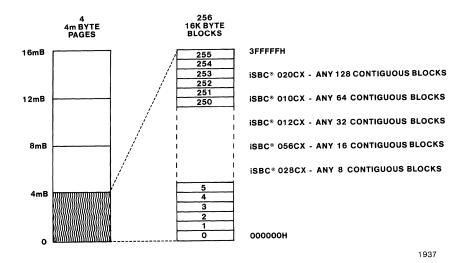

| 2-1.           | MULTIBUS® Page and Base Address Concept                  | 2-5        |

| 2-2.           | MULTIBUS® Base Address Example                           | 2-7        |

| 2-3.           | iSBC@ Ø12CX RAM Board with Deselect Option (Example)     | 2-16       |

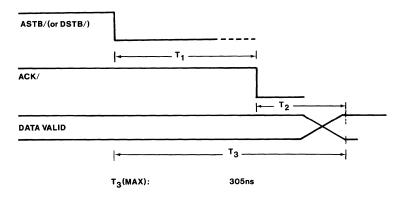

| 2-4.           | iLBX <sup>TM</sup> Bus Acknowledge Time Waveforms        | 2-19       |

| 2-5.           | Jumper Post Location Diagram                             | 2-13       |

| 2-J.<br>4-1.   | Data Path Simplified Diagram                             | 4-4        |

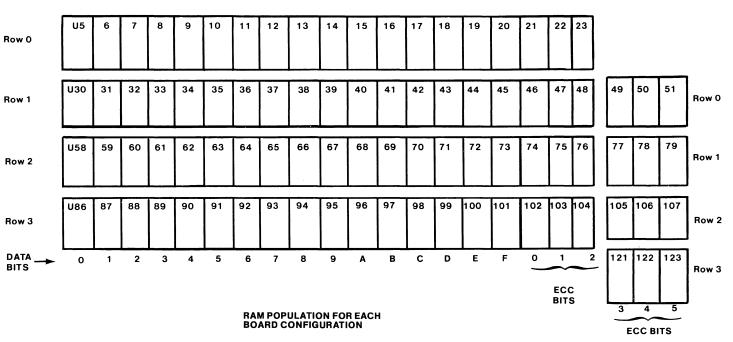

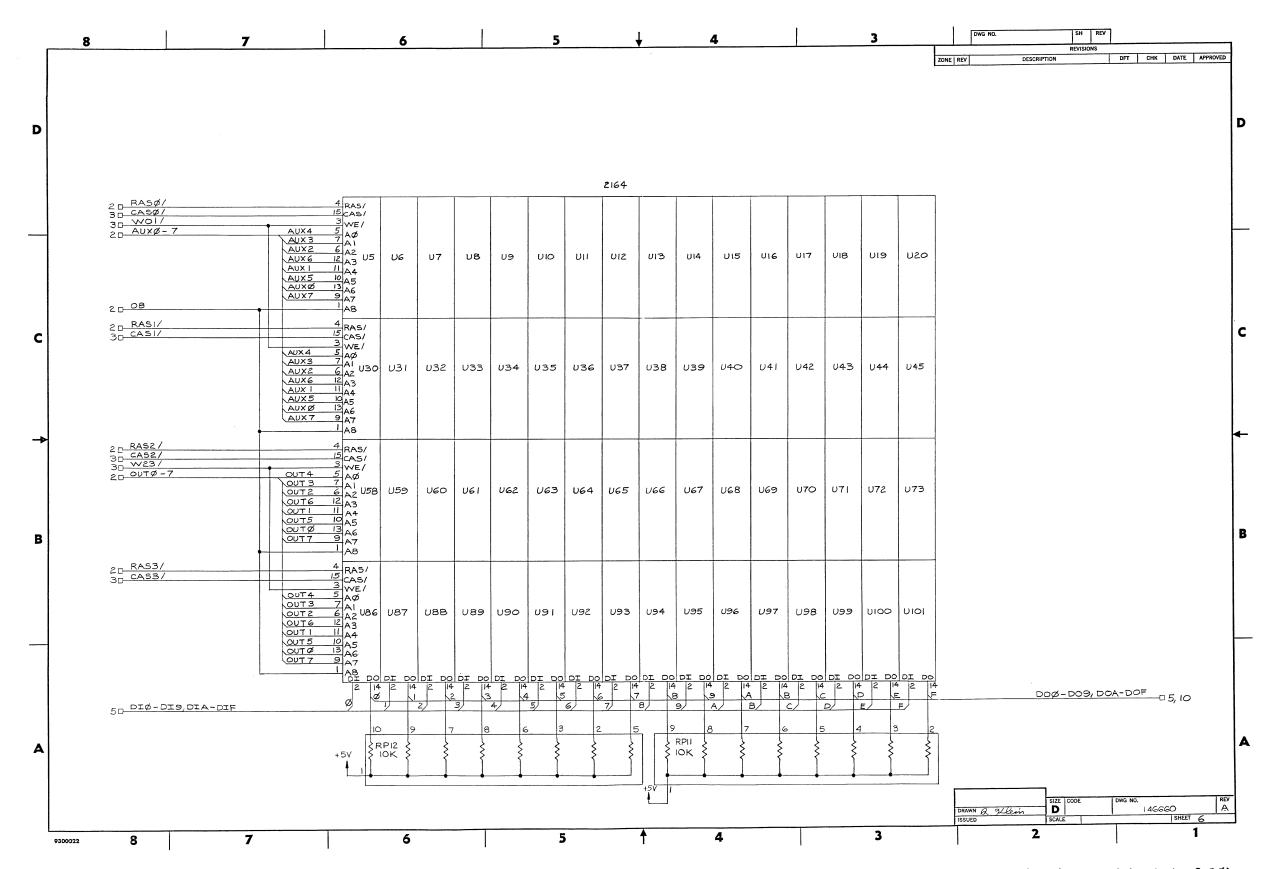

| 5-1.           | iSBC@ CX-Series Boards RAM Device Location Diagram       | 5-3        |

| 5-1.<br>5-2    | isBoo on-series boards while belocation bragiam          | 5-5        |

## CHAPTER 1 GENERAL INFORMATION

#### 1.1 INTRODUCTION

The iSBC CX-Series Random Access Memory (RAM) Boards provide dynamic memory storage capacities of 128K bytes, 256K bytes, 512K bytes, 1024K bytes, and 2048K bytes respectively (Figure 1-1). The boards are compatible in 8-bit or 16-bit systems. The CX-Series of RAM boards uses dynamic RAM devices exclusively, and incorporates error checking and correction (ECC) circuitry on-board. The boards are MULTIBUS and iLBX bus compatible and can be used with battery backup.

Figure 1-1. iSBC@ Ø12CX Random Access Memory Board

#### 1.2 DESCRIPTION

The iSBC CX-Series RAM boards are physically and electrically compatible with the MULTIBUS interface standard as outlined in the INTEL MULTIBUS SPECIFICATION. In addition, the boards feature iLBX bus compatibility. This new Intel Single Board Computer bus is a high-speed extension to the standard MULTIBUS interface. The iLBX bus is described in the INTEL iLBX BUS SPECIFICATION.

The capacity of each RAM board in this series is determined by the type and number of RAM devices on-board. Table 1-1 shows the type and number of devices used for memory and error checking and correction (ECC) on each board. The iSBC Ø28CX, Ø56CX and Ø12CX RAM boards use 64K-bit devices, while the iSBC Ø1ØCX and Ø2ØCX RAM boards use 256K-bit devices.

| Board                | Memory (64K-bit)  | ECC (64K-bit)  |

|----------------------|-------------------|----------------|

| iSBC Ø28CX RAM Board | 16                | 6              |

| iSBC Ø56CX RAM Board | 32                | 12             |

| iSBC Ø12CX RAM Board | 64                | 24             |

|                      | Memory (256K-bit) | ECC (256K-bit) |

| iSBC Ø1ØCX RAM Board | 32                | 12             |

| iSBC Ø2ØCX RAM Board | 64                | 24             |

Table 1-1. Memory and ECC Devices (64K-bit)

Error checking and correcting (ECC) is accomplished with the Intel 8206 Error Detection and Correction Unit and other on-board circuitry. The ECC unit allows detection and correction of single-bit errors, detection of double-bit errors and detection of most multiple-bit errors. As used on this series of boards the ECC circuitry can be programmed to correct all correctable errors (double bit and multiple bit errors are not correctable), or to disregard errors. In addition, the board can be programmed to interrupt the processor on any error or only on non-correctable errors.

Maximum system memory size with this series of boards is 16 megabytes. Memory partitioning is independent for the MULTIBUS interface and the iLBX interface. For MULTIBUS operations, system memory is divided into 4-megabyte pages. On-board jumpers assign the board to one of the four pages. Each page is partitioned into 256 blocks of 16K bytes each. The smallest MULTIBUS partition on any board in this series is 16K bytes. Jumpers assign the base address (lowest 16K block) within the selected 4-megabyte page. The 16K-byte block should not cross the 4-megabyte boundary of the board.

All electrical connections to and from the boards are implemented via edge connectors P1, P2 and J1 (See Appendix A). Connector P1 (86-pin) is the MULTIBUS interface connector and P2 (6 $\emptyset$ -pin) is the iLBX bus connector. Connector J1 is used for battery backup control signals.

#### 1.3 DOCUMENTATION SUPPLIED

Each RAM board is shipped with a current set of schematic diagrams. Keep these diagrams for future reference. The schematic diagrams used in Chapter 5 are for the iSBC Ø12CX RAM board and are used to represent the iSBC Ø28CX/Ø56CX/Ø12CX/Ø1ØCX/Ø2ØCX RAM Boards. For individual board schematics, refer to the set of schematic diagrams shipped with the board.

#### 1.4 SPECIFICATIONS

General specifications for the CX-Series RAM boards are listed in Table 1-2. Refer to the INTEL MULTIBUS SPECIFICATION for board AC and DC specifications and MULTIBUS timing information.

Table 1-2. Specifications

#### **BOARD CAPACITY:**

| iSBC Ø28CX RAM Board: | 128K Bytes (131,072 Bytes)            |

|-----------------------|---------------------------------------|

| iSBC Ø56CX RAM Board: | 256K Bytes (262,144 Bytes)            |

| iSBC Ø12CX RAM Board: | 512K Bytes (524,288 Bytes)            |

| iSBC Ø1ØCX RAM Board: | <u>1024</u> K Bytes (1,048,576 Bytes) |

| iSBC Ø2ØCX RAM Board: | 2048K Bytes (2,097,152 Bytes)         |

#### <u>MULTIBUS MEMORY PARTITIONING</u>: Maximum system RAM size: 16M-bytes

| Page Address (4M bytes): | 1 of 4 pages, as follows: |

|--------------------------|---------------------------|

|                          | Ø – 4 Megabytes           |

|                          | 4 - 8 Megabytes           |

|                          | 8 - 12 Megabytes          |

12 - 16 Megabytes

#### Block Address (16K bytes):

| iSBC Ø28CX RAM Boar<br>iSBC Ø56CX RAM Boar<br>iSBC Ø12CX RAM Boar | rd: 16  | contiguous | 16K-byte | blocks | (128K bytes)<br>(256K bytes)  |

|-------------------------------------------------------------------|---------|------------|----------|--------|-------------------------------|

| iSBC Ø1ØCX RAM Boar                                               |         | _          | •        |        | (512K bytes)<br>(1024K bytes) |

| iSBC Ø2ØCX RAM Boar                                               | rd: 128 | contiguous | 16K-byte | blocks | (2Ø48K bytes)                 |

Note: Blocks cannot cross 4M-byte page boundary. See Section 2.4.1. for MULTIBUS memory addressing.

#### Table 1-2. Specifications (continued)

Base Address: Any 16K-byte boundary with exception of page boundary

REFRESH TIMES:

Refresh Cycle Time:

15.6 usec.

(between refresh cycles)

Refresh Delay Time:

76Ø nsec. maximum

(refresh cycle duration)

MULTIBUS ACCESS TIMES:

Read/Full Write:

35Ø nanoseconds (maximum)

Write Byte:

53Ø nanoseconds (maximum)

Cycle Times:

Read/Full Write:

46Ø nanoseconds

Write Byte:

835 nanoseconds

Note: When an error is detected, read access time & cycle times are

extended by 255 ns (maximum).

iLBX BUS MEMORY PARTITIONING: 2 blocks of 64K bytes each on iSBC Ø28CK

4 blocks of 64K bytes each on iSBC Ø56CX

8 blocks of 64K bytes each on iSBC Ø12CX

16 blocks of 64K bytes each on iSBC Ø1ØCX

32 blocks of 64K bytes each on iSBC Ø2ØCX

Base Address: Any 64K-byte boundary

iLBX ACCESS TIMES: (ASTB/ or DSTB/ to ACK/)

Read/Full Write: Jumper selectable; see section 2.4.7

and Table 2-12 for details

Write Byte: 440 nanoseconds (maximum)

Read Data Access Time: (ASTB/ to Valid Data on iLBX Bus)

3Ø5 nanoseconds (maximum)

Cycle Times:

Read/Full Write: 375 nanoseconds (maximum)

Write Byte: 790 nanoseconds (maximum)

Table 1-2. Specifications (continued)

#### MEMORY PROTECTION/BACKUP:

An active low TTL memory protect signal generated by the power supply, (MPRO/) enters the board via J1. This signal disables read/write access to memory thereby protecting data during system power-down. An optional battery can be used to save data. See section 2.4.8.

#### POWER REQUIREMENTS:

Voltage: 5VDC +5%

Current: iSBC Ø28CX: 6.2A Maximum

iSBC Ø56CX: 6.35A Maximum iSBC Ø12CX: 6.6A Maximum

iSBC Ø1ØCX: 6.45A Maximum

iSBC Ø2ØCX: 6.7A Maximum

Battery Current: iSBC Ø28CX: 2.1A Maximum (Standby mode)

iSBC Ø56CX: 2.2A Maximum (Standby mode) iSBC Ø12CX: 2.4A Maximum (Standby mode) iSBC Ø1ØCX: 2.3A Maximum (Standby mode)

iSBC Ø2ØCX: 2.45A Maximum (Standby mode)

#### **ENVIRONMENTAL REQUIREMENTS:**

Operating Temperature: ذC to 55°C (32°F to 13ذF)

Operating Humidity: To 90% without condensation

tere 85

#### PHYSICAL DIMENSIONS:

Width: 3Ø.48 cm (12.Ø in) Height: 17.15 cm (6.75 in) Thickness: 1.27 cm (Ø.5Ø in)

Weight:

iSBC Ø28CX 469 gm (16.7 oz) iSBC Ø56CX 532 gm (19.Ø oz) iSBC Ø12CX 658 gm (23.5 oz) iSBC Ø1ØCX 532 gm (19.Ø oz) iSBC Ø2ØCX 658 gm (23.5 oz)

#### 1.5 COMPLIANCE LEVEL: 796 BUS SPECIFICATION (IEEE STANDARD)

All Intel MULTIBUS-compatible boards are designed around guidelines set forth in the 796 BUS SPECIFICATION (IEEE STANDARD - formerly the INTEL MULTIBUS SPECIFICATION). The standard requires that certain board operating characteristics, such as data bus width and memory addressing paths, be clearly stated in the board's printed specifications (i.e.,

reference manual). Used properly, this information quickly summarizes the level of compliance the board bears to the published 796 BUS SPECIFICATION. It clearly states the board's level of compatibility to the MULTIBUS structure. Refer to the 796 BUS SPECIFICATION or the INTEL MULTIBUS SPECIFICATION for additional information.

The following notation states the iSBC CX-Series RAM board's level of compliance to the 796 BUS SPECIFICATION:

D16 M24 I8

This notation is decoded as follows:

D16 = data path is 8 and/or 16 bits

M24 = memory address path is up to 24 bits

I8 = I/O address path is 8 bits

#### 1.6 ilbx™ bus compliance level

All Intel iLBX bus-compatible boards are designed around guidelines set forth in the INTEL iLBX BUS SPECIFICATION. The specification requires that certain board operating characteristics, such as data path width, address path width, and other characteristics, be clearly stated in the board's printed specifications (i.e., reference manual). Used properly, this information quickly summarizes the level of compliance the board bears to the published specification. It clearly states the board's level of compatibility to the iLBX bus structure. Refer to the INTEL iLBX BUS SPECIFICATION for more information.

The compliance level for the iSBC CX-Series RAM Boards is as follows:

**SL D16**

SL indicates the board is a slave board, and D16 indicates a 16-bit data path width.

## CHAPTER 2 PREPARATION FOR USE

#### 2.1 INTRODUCTION

This chapter provides instructions for preparing the iSBC CX-Series RAM Boards for use in various environments. Included in this chapter are instructions on unpacking and inspection, installation considerations such as physical dimensions and cooling requirements; jumper configurations; and battery back-up configuration.

#### 2.2 UNPACKING AND INSPECTION

Inspect the shipping carton immediately upon receipt for evidence of mishandling during transit. If the shipping carton is severely damaged or waterstained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is not present when the carton is opened and the contents of the carton are damaged, keep the carton and the packing material for the agent's inspection.

For repair to a product damaged in shipment, contact the Intel Technical Support Center to obtain a Return Authorization Number and further instructions. A purchase order is required to complete the repair. A copy of the purchase order should be submitted to the carrier with your claim.

Save the salvageable shipping cartons and packing material for future use in the event that the board must be shipped.

#### 2.3 INSTALLATION CONSIDERATIONS

Installation considerations such as power, cooling, physical size requirements, and interfacing requirements are outlined in the following paragraphs.

#### 2.3.1 POWER REQUIREMENTS

The power requirements for the RAM boards depend on quantity and type of RAM chips installed onto the RAM boards. See Table 1-2 in Chapter 1 for the various current requirements for each configuration of the RAM boards.

#### 2.3.2 COOLING REQUIREMENTS

The heat dissipation for the RAM boards varies with the configuration of the board; Table 2-1 shows the maximum power dissipation for each configuration. Adequate circulation of air must be provided to prevent a

temperature rise above  $55^{\circ}$ C ( $130^{\circ}$ F). Typically, a minimum air flow of 200 linear feet per minute at an inlet temperature no higher than  $55^{\circ}$ C provides enough air circulation to maintain the air temperature around the CX-Series RAM Boards within this limit.

Table 2-1. Heat Dissipation

| Board                                                  | Dissipation                                                                                                                                      |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| iSBC Ø28CX iSBC Ø56CX iSBC Ø12CX iSBC Ø1ØCX iSBC Ø2ØCX | 463 gm-cal/minute (1.87 Btu) 47ø gm-cal/minute (1.9ø Btu) 484 gm-cal/minute (1.96 Btu) 47ø gm-cal/minute (1.9ø Btu) 484 gm-cal/minute (1.96 Btu) |

#### 2.3.3 MULTIBUS® INTERFACING REQUIREMENTS

The iSBC CX-Series RAM Boards are designed for installation into a standard Intel iSBC cardcage or into an Intel Microcomputer Development System chassis. The 86-pin edge connector (P1) on the RAM boards provides interfacing to the MULTIBUS structure. Appendix A lists the pin assignments for connector P1.

Edge connector P2 on the RAM boards is used for the iLBX bus control, data, and address lines. MULTIBUS battery back-up signals, and memory protection signals for the RAM boards are routed through connector J1, which is located in the upper right-hand corner of the board. Appendix A lists the pin assignments for connector P2 and connector J1.

#### 2.4 JUMPER CONFIGURATIONS

The iSBC CX-Series RAM board is shipped from the factory with a specific default jumper configuration. The default configuration may require alteration to suit your particular application. The following sections describe the user jumper configurations in their default state and optional states.

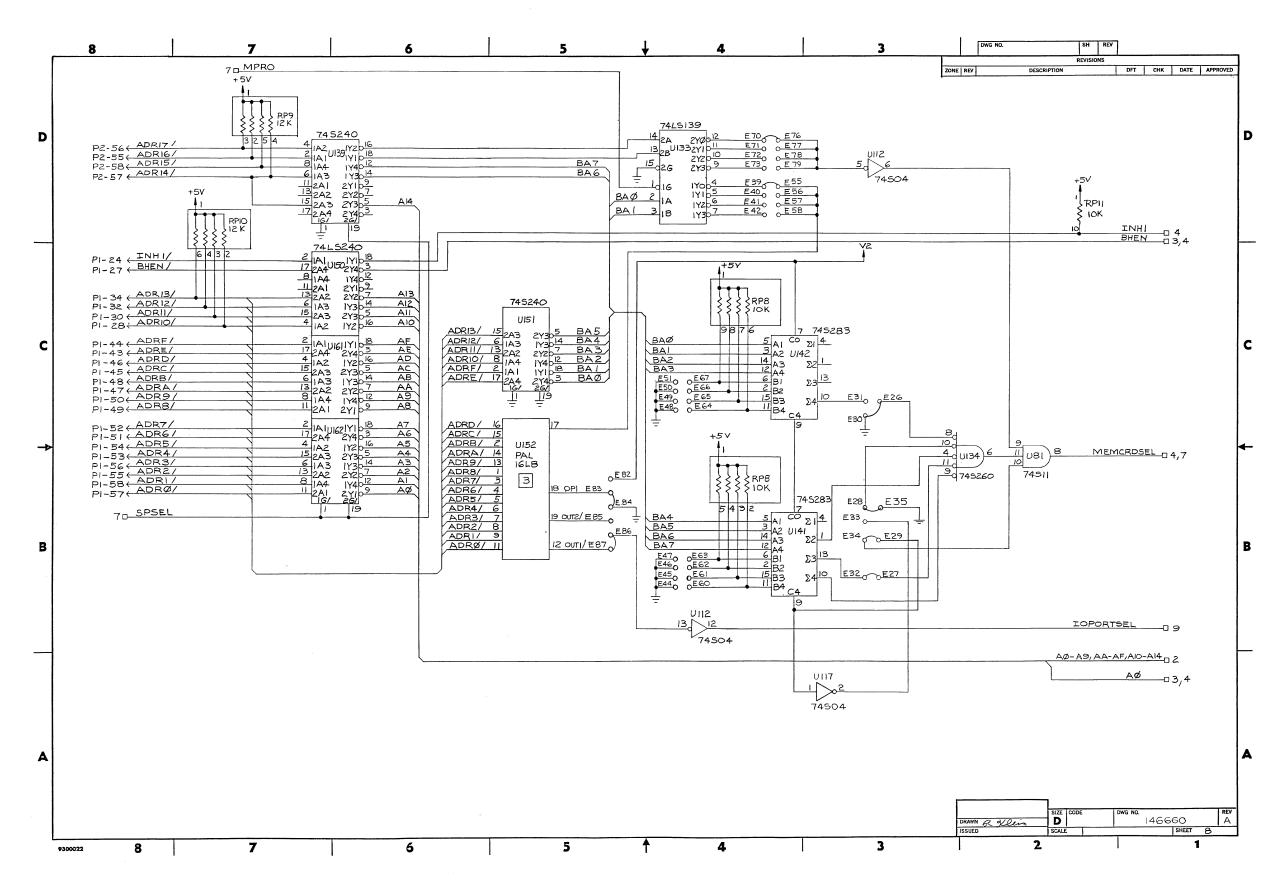

#### 2.4.1 MULTIBUS® MEMORY ADDRESSING

The iSBC CX-Series RAM boards support several MULTIBUS addressing modes: 16-bit, 20-bit, and 24-bit addressing. The board is structured to accept 24-bit address words, on MULTIBUS lines ADR0/ through ADR17/. The two most significant lines (ADR16/ and ADR17/) are used to select a particular 4-megabyte page of addresses. This allows a maximum of 4-megabytes of direct addressing capability, using the remaining 22

address lines (ADR15/ through ADRØ/). When a RAM board is installed in a system, selectable jumpers specify where within the overall 16-megabyte MULTIBUS address space the board is to reside.

Systems with 2Ø address lines should interface directly to MULTIBUS address lines ADRØ/ through ADR13/. This scheme allows addressing of up to 1 megabyte of memory (ØH through ØFFFFFH). Systems with 16 address lines should interface directly to MULTIBUS address lines ADRØ/ through ADRF/. This configuration allows addressing of up to 64K-bytes of memory (ØH through ØØFFFFH).

Four additional address lines are available on connector P2. These are MULTIBUS address lines ADR14/ through ADR17/. Address lines ADR14/ and ADR15/ are used for decoding up to 4 megabytes of memory; lines ADR16/ and ADR17/ are used for full 16-megabyte direct addressing on fully compatible systems.

For universal addressing compatibility, MULTIBUS address lines ADR10/through ADR17/ are held high (+5VDC) with on-board pull-up resistors. Memory board operation will not be adversely affected if these lines are not used or connected in your system.

In order to select the correct address jumpers for your application, you must consider the overall addressing scheme for this board. MULTIBUS memory address jumpers are configured with two sets of jumpers. The first set selects the particular 4-megabyte page within which the board is to reside. The second set of jumpers selects the base (starting) address for the board, within the selected page. Refer to Section 2.4.1.2 for more information.

When configuring the board for your application first examine the current status of the board. Your application may require changing only one jumper. Typically, the base address selection jumpers will be the most likely to change from application to application. The board is defaulted to the lowest base address  $(\emptyset\emptyset\emptyset\emptyset\emptyset\emptyset\emptyset)$  in page  $\emptyset$ ).

The following sub-sections discuss the four MULTIBUS address jumper sets in more detail. Refer to Figure 2-5 for the physical location of the jumpers on the board.

#### 2.4.1.1 MULTIBUS® Page Address Selection Jumpers

This set of jumpers is used to select the 4-megabyte page in which the board is to reside. MULTIBUS memory allows 16-megabytes, so there are four choices. These choices are shown in Table 2-2. The board will respond only to the code (formed by ADR16/ and ADR17/) which matches the jumper selected page, as described in section 2.4.1. The board is defaulted to page  $\emptyset$ .

Table 2-2. MULTIBUS® Page Select Jumpers

| Jumper Pair | Function                    |

|-------------|-----------------------------|

| 7ø - 76 §   | Page Ø (Ø to 4 megabytes)   |

| 72 - 78     | Page 1 (4 to 8 megabytes)   |

| 71 - 77     | Page 2 (8 to 12 megabytes)  |

| 73 – 79     | Page 3 (12 to 16 megabytes) |

|             | <u>.</u>                    |

Note: § = Default Configuration (jumpers installed).

#### 2.4.1.2 MULTIBUS® Base Address Jumpers

The 4-megabyte memory page selected with the jumpers in Section 2.4.1.1 consists of 256 individual 16-kilobyte blocks. Block Ø is located at the lowest point of the 4-megabyte page and block 255 is located at the highest point in the 4-megabyte page. Figure 2-1 illustrates this concept.

Board capacity determines how many of the 256 blocks are used. The iSBC Ø28CX board uses any 8 contiguous blocks; the iSBC Ø56CX board uses any 16 contiguous blocks; the iSBC Ø12CX board uses any 32 contiguous blocks; the iSBC Ø1ØCX board uses any 64 contiguous blocks; and the iSBC Ø2ØCX board uses any 128 contiguous blocks. Refer to Figure 2-1.

The base address is defined as the starting point of the lowest block you select. Board memory will then continue upward for the number of contiguous blocks according to capacity. Any 16K-byte block can be selected for a base address. The base address is set by creating an eight-bit binary value with the base address selection jumpers. Installing a jumper in one of the digits equals a binary 1; conversely, absence of a jumper equals a binary  $\emptyset$ . Table 2-3 correlates the jumpers to their binary equivalents.

The selected memory space cannot cross a 4-megabyte page boundary. Any 16K-byte blocks extending into the next 4-megabyte page, will wrap around to the beginning of the memory page in which the base address block exists. For example, if you want your base address to be at block 17,

you would install jumpers between posts 47-63 and 51-67. This is a binary value of  $\emptyset\emptyset\emptyset1\emptyset\emptyset\emptyset1$  or 17 decimal. Assuming you had a iSBC  $\emptyset28CX$  board (128K-bytes capacity), your address space would extend from the first byte in block 17 through the last byte in block 24 for a total of eight 16K-byte blocks. This is equivalent to addresses  $44\emptyset\emptyset\emptysetH-63FFFH$ .

#### NOTE

Remember that on-board RAM is shared by MULTIBUS memory and iLBX bus memory. Because of this sharing, we recommend that the address space selected for each bus fully overlap. For example, if the MULTIBUS base address is set to 512K bytes, then the iLBX bus base address should also be set to 512K bytes. If the memory is partially overlapped, or not overlapped at all, iLBX bus data could be written into different MULTIBUS locations under certain conditions.

Figure 2-1. MULTIBUS@ Page and Base Address Concept

Another example of base address selection on an iSBC  $\emptyset$ 12CX board is shown in Figure 2-2. See Section 2.4.1.4 for iLBX bus addressing jumper configurations.

Table 2-3. MULTIBUS® Base Address Selection Jumpers

| Jumper Pair                                                                          | Function                                                                                                                                                                               |  |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 44 - 6Ø<br>45 - 61<br>46 - 62<br>47 - 63<br>48 - 64<br>49 - 65<br>5Ø - 66<br>51 - 67 | Base Address Bit 7 (MSB) Base Address Bit 6 Base Address Bit 5 Base Address Bit 4 Base Address Bit 3 Base Address Bit 2 Base Address Bit 1 Base Address Bit 1 Base Address Bit Ø (LSB) |  |

Note: Default configuration is all jumpers out (removed).

(Jumper IN = 1; Jumper OUT = Ø)

#### iSBC® 012CX RAM BOARD CONFIGURATION-MULTIBUS® (512K BYTES) SYSTEM 16mB 256x16K BLOCK 4-mB SYSTEM ADDRESS MULTIBUS® 32x16K BLOCK 8mB 31 47FFFFH 30 47BFFFH 12mB ADDRESS OF LAST BYTE IN BLOCK 29 477FFFH 7mB 28 473FFFH 46FFFFH 27 26 46BFFFH 8mB 6mB 5 414000H 4mB 5mB 4 410000H ADDRESS OF FIRST BYTE IN BLOCK 40C000H 3 2 408000H 0 1 404000H JUMPER SELECT 72-78 PAGE 1 4mB 0 400000H MULTIBUS® BASE ADDRESS SELECTION JUMPERS (NONE) BASE ADDRESS 400000H SELECTS ANY 32 CONTIGUOUS BLOCKS 0-31 IN THIS EXAMPLE 1938

Figure 2-2. MULTIBUS® Base Address Example

#### 2.4.1.3 iLBX™ Bus Memory Addressing

The iLBX bus memory address space consists of 256 contiguous blocks of 64K bytes each. This is a total of 16 megabytes of memory. As shipped from the factory, each board is configured so that the board starts at address ØØØØØØH, and continues upward for the number of contiguous 64K-byte blocks allowed for its capacity. The iSBC Ø28CX board occupies 128K bytes (ØØØØØØH to 1FFFFFH); the iSBC Ø56CX board occupies 256K bytes (ØØØØØØH to 3FFFFH); the iSBC Ø12CX board occupies 512K bytes (ØØØØØØH to 7FFFFH); the iSBC Ø1ØCX board occupies 1Ø24K bytes (ØØØØØØH to FFFFFH); and the iSBC Ø2ØCX board occupies 2Ø48K bytes (ØØØØØØH to 1FFFFFH).

#### 2.4.1.4 iLBX™ Bus Base Address And Address Range Jumpers

The iLBX base address and address range is a function of on-board Programmed Array Logic (PAL) device U158 and the iLBX base address and range jumpers selected. Three jumpers are used to select the iLBX base address and address range. The default iLBX base address for the CX-Series boards is zero (000000H).

The memory boards examine iLBX address lines AB10 - AB17 to determine if the address on the iLBX bus refers to on-board memory. If more than one iLBX memory board is used in your system, ensure that the address ranges of the boards do not cause memory space overlapping. There are 21 pre-programmed address ranges for the iSBC Ø28CX/Ø56CX boards; 28 for the iSBC Ø12CX board; and 14 for the iSBC Ø10CX/Ø20CX boards.

The pre-programmed PAL can be replaced with the users PAL, which can then be programmed to provide additional address ranges for the board. See Appendix B for current PAL code.

Tables 2-4, 2-5, 2-6, 2-7, and 2-8 correlate the jumper connections to the iLBX address range selection for the iSBC CX-Series RAM Boards.

Table 2-4. iLBX<sup>TM</sup> Bus Address Range Jumpers

| I               |                        |                    |                    |                               |  |

|-----------------|------------------------|--------------------|--------------------|-------------------------------|--|

| Jumpers         | 1Ø6-1Ø7 §<br>1Ø9-11Ø § | 1Ø6-1Ø7<br>11Ø-111 | 1Ø7-1Ø8<br>1Ø9-11Ø | 1Ø7-1Ø8<br>11Ø-111            |  |

| 91-99 §         | øøøøøø–ø1ffff          | øeøøøø-øfffff      | 1CØØØØ-1DFFFF      | User                          |  |

| 92-1øø          | ø2øøøø-ø3ffff          | 1øøøøø–11ffff      | 1EØØØØ-1FFFF       | Programmable<br>w/ User's PAL |  |

| 93–1ø1          | ø4øøøø–ø5ffff          | 12ØØØØ-13FFFF      | 2ØØØØØ-21FFFF      |                               |  |

| 94-1Ø2          | ø6øøøø-ø7ffff          | 14ØØØØ-15FFFF      | 22ØØØØ-23FFFF      |                               |  |

| 95–1ø3          | Ø8ØØØØ-Ø9FFFF          | 16ØØØØ-17FFFF      | 24ØØØØ-25FFFF      |                               |  |

| 96-1Ø4          | ØAØØØØ-ØBFFFF          | 18ØØØØ-19FFFF      | 26ØØØØ-27FFFF      |                               |  |

| 97 <b>–1</b> Ø5 | ØCØØØØ-ØDFFFF          | 1AØØØØ–1BFFFF      | 28ØØØ-29FFFF       |                               |  |

Notes: § - Indicates default jumper.

All addresses in Hexadecimal.

Table 2-5. iLBX<sup>TM</sup> Bus Address Range Jumpers

|         | iSBC@ Ø56CX 256K RAM Board |                       |                    |                               |

|---------|----------------------------|-----------------------|--------------------|-------------------------------|

| Jumpers | 1Ø6-1Ø7 §<br>1Ø9-11Ø §     | 1Ø6-1Ø7<br>11Ø-111    | 1Ø7–1Ø8<br>1Ø9–11Ø | 1Ø7-1Ø8<br>11Ø-111            |

| 91-99 § | øøøøøø–ø3ffff              | 1CØØØØ-1FFFFF         | 38øøøø-3bffff      | User                          |

| 92–1øø  | Ø4ØØØØ-Ø7FFFF              | 2ØØØØØ-23FFFF         | 3CØØØØ-3FFFFF      | Programmable<br>w/ User's PAL |

| 93–1ø1  | Ø8ØØØØ-ØBFFFF              | 24ØØØØ-27FFFF         | 4ØØØØØ-43FFFF      |                               |

| 94-1Ø2  | ØCØØØØ-ØFFFFF              | 28ØØØØ-2BFFFF         | 44ØØØØ-47FFFF      |                               |

| 95–1ø3  | 1øøøøø–13ffff              | 2CØØØØ-2FFFF          | 48øøøø-4BFFFF      |                               |

| 96-1Ø4  | 14ØØØØ-17FFFF              | 3 <b>øøøø</b> ø-33fff | 4CØØØØ-4FFFF       |                               |

| 97–1Ø5  | 18øøøø–1BFFFF              | 34ØØØØ-37FFFF         | 5øøøøø–53ffff      |                               |

Notes: § - Indicates default jumper.

All addresses are in Hexadecimal.

Table 2-6. iLBX™ Bus Address Range Jumpers

|                 | iSBC@ Ø12CX 512K RAM Board |                       |                        |                    |

|-----------------|----------------------------|-----------------------|------------------------|--------------------|

| Jumpers         | 1Ø6-1Ø7 §<br>1Ø9-11Ø §     | 1Ø6-1Ø7<br>11Ø-111    | 1Ø7–1Ø8<br>1Ø9–11Ø     | 1Ø7-1Ø8<br>11Ø-111 |

| 91-99 §         | øøøøøø-ø7ffff              | 38øøøø–3fffff         | 7 <b>ØØØØØ</b> -77FFFF | øøøøøø–ø5ffff¶     |

| 92–1øø          | Ø8ØØØØ-ØFFFFF              | 4 <b>00000</b> -47FFF | 78ØØØØ-7FFFF           | Ø1ØØØØ-Ø8FFFF      |

| 93–1ø1          | 1øøøøø-17ffff              | 48øøøø–4ffff          | 8øøøøø-87fff           | Ø2ØØØØ-Ø9FFFF      |

| 94-1Ø2          | 18øøøø–1ffff               | 5øøøøø–57ffff         | 88øøøø–8ffff           | ø3øøøø-øaffff      |

| 95–1ø3          | 2ØØØØØ–27FFFF              | 58øøøø-5ffff          | 9øøøøø-97ffff          | ø4øøøø-øbffff      |

| 96-1Ø4          | 28øøøø–2ffff               | 6øøøøø-67ffff         | 98 <b>øøø</b> ø-9ffff  | Ø5ØØØØ-ØCFFFF      |

| 97 <b>–1</b> Ø5 | 3ØØØØØ-37FFFF              | 68ØØØØ-6FFFFF         | AØØØØØ-A7FFFF          | Ø6ØØØØ-ØDFFFF      |

- Notes: § Indicates default jumper.

- $\P$  Indicates this configuration is memory deselected, the full memory capacity is not addressed.

All addresses are in Hexadecimal.

Table 2-7. iLBX™ Bus Address Range Jumpers

|         | iSBC@ Ø1ØCX 1M RAM Board |                      |                      |                    |  |

|---------|--------------------------|----------------------|----------------------|--------------------|--|

| Jumpers | 1Ø6-1Ø7 §<br>1Ø9-11Ø §   | 1Ø6-1Ø7<br>11Ø-111   | 1Ø7-1Ø8<br>1Ø9-11Ø   | 1Ø7-1Ø8<br>11Ø-111 |  |

| 91-99 § | øøøøøø–øfffff            | User<br>Programmable | User<br>Programmable | øøøøøø-øcffff ¶    |  |

| 92–1øø  | 1øøøøø–1fffff            | w/ User's PAL        | w/ User's PAL        | øøøøøø-ødffff¶     |  |

| 93–1ø1  | 2ØØØØØ-2FFFF             |                      |                      | øøøøøø–øeffff ¶    |  |

| 93–1ø2  | 3ØØØØØ-3FFFF             |                      |                      | ØCØØØØ-1BFFFF      |  |

| 95–1ø3  | 4ØØØØØ–4FFFF             |                      |                      | 1ØØØØØ-1FFFFF      |  |

| 96-1ø4  | 5øøøøø-5ffff             |                      |                      | 14ØØØØ-23FFFF      |  |

| 97–1ø5  | 6ØØØØØ–6FFFFF            | :                    |                      | 18ØØØØ-27FFFF      |  |

Notes: § - Indicates default jumper.

$\P$  - Indicates this configuration is memory deselected, the full memory capacity is not addressed.

All addresses are in Hexadecimal.

Table 2-8. iLBX™ Bus Address Range Jumpers

|         | iSBC@ Ø2ØCX 2M RAM Board |                      |                      |                    |  |

|---------|--------------------------|----------------------|----------------------|--------------------|--|

| Jumpers | 1Ø6-1Ø7 §<br>1Ø9-11Ø §   | 1ø6-1ø7<br>11ø-111   | 1Ø7-1Ø8<br>1Ø9-11Ø   | 1Ø7-1Ø8<br>11Ø-111 |  |

| 91-99 § | øøøøøø-ø1fffff           | User<br>Programmable | User<br>Programmable | øøøøøø–ødffff ¶    |  |

| 92–1øø  | 2ØØØØØ-Ø3FFFFF           | w/ User's PAL        | w/ User's PAL        | Ø1ØØØØ-2ØFFFF      |  |

| 93–1ø1  | 4øøøøø-ø5fffff           |                      |                      | Ø2ØØØØ-21FFFF      |  |

| 94-1ø2  | 6ØØØØØ-Ø7FFFF            |                      |                      | 1øøøøø-2ffff       |  |

| 95–1ø3  | 8øøøøø–ø9ffff            |                      |                      | Ø8ØØØØ-9FFFFF      |  |

| 95–1ø4  | AØØØØØ-ØBFFFFF           |                      |                      | ØAØØØØ-BFFFFF      |  |

| 97–1ø5  | CØØØØØ-ØDFFFFF           |                      |                      | ØCØØØØ-DFFFFF      |  |

Notes: § - Indicates default jumper.

¶ - Indicates this configuration is memory deselected, the full memory capacity is not addressed.

All addresses in Hexadecimal.

#### 2.4.1.5 Memory Deselect (iSBC® 012CX/010CX/020CX RAM Boards Only)

The iSBC Ø12CX/Ø1ØCX/Ø2ØCX boards allow deselection of portions of their upper addressed memory. This allows the memory size of a board to look smaller than it physically is. This option, however, forces the base address of the board to zero. One possible use for the deselected address space is a memory location for other memory-mapped boards. While it is possible to deselect the MULTIBUS independently from the iLBX bus, it is not recommended due to the deselected memory addresses being accessible only by the iLBX bus.

To deselect memory from the iLBX bus, choose the jumper options for deselect listed in Table 2-6, 2-7 or 2-8 for the iSBC  $\emptyset12CX/\emptyset1\emptysetCX/\emptyset2\emptysetCX$  RAM Boards. For example, on an iSBC  $\emptyset12CX$  board, choosing the jumper option of  $1\emptyset7-1\emptyset8$  and  $11\emptyset-111$  along with 91-99 sets-up a base address of  $\emptyset$ H with the upper 128K bytes deselected. This causes the board to respond only to memory addresses  $\emptyset$ H through 5FFFFH.

Deselection of memory from the MULTIBUS system is accomplished differently. First, the MULTIBUS Deselection option must be selected by the following jumper modifications:

Remove Jumper: 29-34

Install Jumper: 33-34

Next, the size of the memory segment deselected is defined by the MULTIBUS Address Range Selection jumpers. The size is set by creating an eight-bit binary value with the address range selection jumpers. The size of the memory segment deselected is equal to the eight-bit binary value, plus one, in 16K-byte blocks. In this configuration, a jumper installed is a  $\emptyset$ , and a jumper removed is a 1 (see table 2-9).

For example, performing the following jumper modifications sets-up a MULTIBUS address range of ØØØØØØH through 5FFFFH on an iSBC Ø12CX board:

Remove Jumper: 34-29

Install Jumper: 34-33

34-33 48-64 47-63 46-62 45-61 44-6Ø

In this example, the eight-bit binary value ØØØØØ111 is formed on the Address Range Selection Jumpers. This deselects the top 8 (7 plus 1) 16K-byte segments, or 128K bytes total. This causes the board to respond only to memory addresses ØØØØØØH through 5FFFFH. Figure 2-3 shows the deselect option along with the jumper modifications. Once again, remember that memory deselected boards always start at a base address of zero.

Table 2-9. MULTIBUS® Address Range Selection Jumpers with Deselect Option (Jumper 33-34)

|      | Jumper Pair | Function           |

|------|-------------|--------------------|

| MSB) | 44-6Ø       | Base Address Bit 7 |

|      | 45-61       | Base Address Bit 6 |

|      | 46-62       | Base Address Bit 5 |

|      | 47–63       | Base Address Bit 4 |

|      | 48-64       | Base Address Bit 3 |

|      | 49-65       | Base Address Bit 2 |

|      | 5Ø-66       | Base Address Bit 1 |

| LSB) | 51-67       | Base Address Bit Ø |

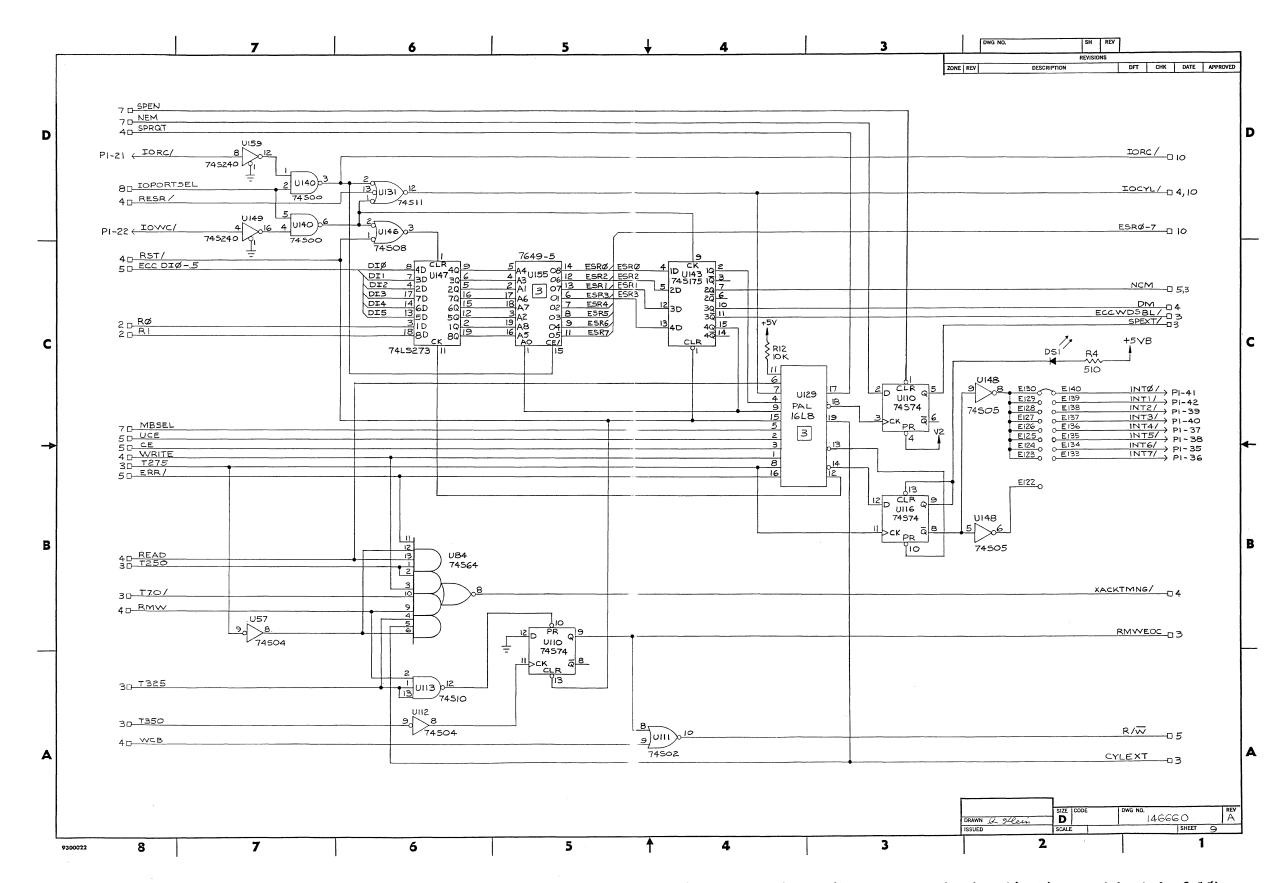

#### 2.4.2 ECC I/O ADDRESS SELECTION

The Error Checking and Correction (ECC) circuitry communicates with the processor board through a single I/O port. This port is used for the Control Status Register (CSR) and the Error Status Register (ESR). The iSBC CX-Series RAM board is shipped with a Programmed Array Logic (PAL) device (U152) which allows selecting one of nine possible addresses for the I/O port. The actual selection is done by jumper configuration. If your application requires an I/O address which is not listed in Table 2-10, the PAL at location U152 must be replaced and the user's PAL reprogrammed (refer to Appendix B).

Three sets of jumpers are used to select the desired I/O address that the board will recognize. Table 2-10 illustrates the nine possible addresses and indicates the default I/O address (01C0H). The table shows how to assign one of the nine addresses to the board, using the three sets of jumpers.

#### CONFIGURES ISBC® 012CX RAM BOARD FOR ADDRESS RANGE 00000H-5FFFFH (128K BYTES DESELECTED) JUMPER MODIFICATIONS 31 30 FOR iLBX™ BUS: 29 REMOVE: 106-107 28 NORMAL BOARD SIZE IS 32 x 16K BLOCKS, BUT TOP 8 BLOCKS ARE DESELECTED INSTALL: 107-108 110-111 27 26 25 FOR MULTIBUS®: 24 REMOVE: 29-34 LAST BYTE 5FFFFH 23 22 INSTALL: 33-34 44-60 45-61 46-62 47-63 48-64 21 6 5 4 3 2 1 FIRST BYTE 00000H 0 1939

Figure 2-3. iSBC@ Ø12CX RAM Board with Deselect Option (Example)

Table 2-10. I/O Address Jumpers

| Jumpers (IN)                       | 86-87 §                          |                                  | 85–86         |                      |

|------------------------------------|----------------------------------|----------------------------------|---------------|----------------------|

|                                    | 83-84 <b>§</b>                   | 82-83                            | 83-84         | 82–83                |

| 39-55 §<br>4Ø-56<br>41-57<br>42-58 | Ø1CØH<br>41CØH<br>81CØH<br>C1CØH | Ø1C1H<br>41C1H<br>81C1H<br>C1C1H | <b>ø</b> ø4øн | User<br>Programmable |

Note: § - Indicates default jumper configuration.

#### 2.4.3 ilbx<sup>™</sup> bus interface address strobe jumper

The memory board is shipped from the factory configured for iLBX bus <u>and MULTIBUS</u> operation. If your application is <u>MULTIBUS-ONLY</u>, install the following jumper:

9Ø - 98

#### 2.4.4 iLBX™ BUS SPEED SELECTION JUMPER

In the default configuration (as-shipped), the iLBX Bus interface on the CX-Series boards operates in fast mode. In fast mode, the iLBX cycle starts after ASTB/ becomes active. In slow mode, an iLBX cycle is not started until both ASTB/ and DSTB/ have become active. To enable the slow mode, perform the following jumper modifications:

Remove Jumper: 10-11 Install Jumper: 11-12

#### 2.4.5 INTERRUPT LEVEL SELECTION JUMPERS

The on-board ECC circuitry will generate an interrupt as specified in Section 3.2. The interrupt can be placed on a jumper-selected MULTIBUS interrupt line. Jumpers are used to specify the interrupt level and MULTIBUS line. The default setting for the interrupt is INTØ/. Table 2-11 provides a list of all the interrupt lines and jumpers. Push-on jumper headers are used to select the interrupt level, as shown in Table 2-11.

Whenever an interrupt is generated the on-board indicator lamp (LED) will illuminate. This lamp can be used for test and diagnostic purposes.

Table 2-11. Interrupt Level Selection Jumpers

| Jumper Pair                                                                       | Level                                                                | MULTIBUS@ Pin                                                                        |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| 13Ø - 14Ø § 129 - 139 128 - 138 127 - 137 126 - 136 125 - 135 124 - 134 123 - 133 | INTØ/<br>INT1/<br>INT2/<br>INT3/<br>INT4/<br>INT5/<br>INT6/<br>INT7/ | P1 - 41<br>P1 - 42<br>P1 - 39<br>P1 - 4Ø<br>P1 - 37<br>P1 - 38<br>P1 - 35<br>P1 - 36 |

Note: § - Indicates default jumper configuration; jumper installed.

#### 2.4.6 EXTERNAL REFRESH (REFRQST) JUMPER

The iSBC CX-Series RAM boards are configured at the factory for on-board refresh. If an external, off-board refresh is needed for test purposes, it is possible to disable the on-board refresh circuitry. The iLBX bus cannot be used if an external refresh is employed as the refresh pins are defined by the iLBX connector. To enable external refresh, perform the following modifications:

- a. Remove jumper 5 6.

- b. Install jumper 4 5.

- c. Install jumper 141 142.

- d. Connect the external refresh signal to pin 40 of connector P2.

#### 2.4.7 ilbx<sup>IM</sup> bus acknowledge time selection jumpers

The iSBC CX-Series RAM boards acknowledge time for iLBX bus requests can be optimized for a given master-slave (host board, CX-Series board) application. Table 2-12 provides acknowledge times for the CX-Series boards and their associated jumper connections. Figure 2-4 illustrates the timing waveforms for the iLBX Bus Acknowledge activity.

In optimized mode, the master-slave timing relationship is selected for Read cycles. Refer to the INTEL iLBX BUS SPECIFICATION for additional details on optimized operation. Also refer to the Acknowledge Acceptance Times for the host board as well as Figure 2-4 and Table 2-12 to select the optimum acknowledge time for your given application.

The iLBX Read cycle is started by ASTB/ (or DSTB/ if in slow mode). The time interval between ASTB/ (or DSTB/) from the master and the acknowledge signal (ACK/) from the slave is defined as T1, and is jumper selectable to meet the masters minimum wait-state requirements. The minimum time for T1 must be greater than the maximum value of ASTB/ to DSTB/ + 10 nanoseconds.

T1 and T2 Times: See Table 2 - 12.

1103

Figure 2-4. iLBX™ Bus Acknowledge Time Waveforms

The maximum time from ACK/ to when valid data is present is defined as T2, and is also a function of the jumpers selected. This time must also match the masters timing requirements, as the master cannot read data before it is valid.

The maximum time from ASTB/ to data valid is defined as T3 and is a maximum of 3Ø5 nanoseconds. T3 is independent of ACK/ timing and is not jumper selectable.

### PREPARATION FOR USE

Table 2-12. Acknowledge Time Selection Jumpers

| Jumpers                                                          | T1 Min                                             | Tl Max                                             | T2 Max                                         |

|------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|------------------------------------------------|

| 38 - 68 <u>and</u> :                                             |                                                    |                                                    |                                                |

| 17 - 16<br>17 - 7<br>17 - 9<br>17 - 8                            | 65ns<br>82ns<br>92ns<br>1Ø1ns                      | 117ns<br>138ns<br>148ns<br>159ns                   | 212ns<br>193ns<br>183ns<br>174ns               |

| 68 - 54 ¶                                                        | 135ns                                              | 196ns                                              | 14Øns                                          |

| 43 - 59 § <u>and</u> :                                           |                                                    |                                                    |                                                |

| 68 - 69 §<br>68 - 36<br>68 - 74<br>68 - 75<br>68 - 53<br>68 - 37 | 2Ø6ns<br>23Øns<br>254ns<br>278ns<br>3Ø1ns<br>325ns | 274ns<br>3Ø1ns<br>327ns<br>353ns<br>379ns<br>4Ø6ns | 69ns<br>45ns<br>21ns<br>-3ns<br>-26ns<br>-5Øns |

Notes: § - Default jumper configuration.

¶ - Installing this jumper only, gives the times stated.

A negative time indicates that T2 is occurring after data is valid.

### 2.4.8 BATTERY BACK-UP AND MEMORY SAVE JUMPERS

In systems employing a battery back-up and memory save feature, the user must interface to connector Jl. The system power supply must generate some type of power-failure signal, for full MULTIBUS compatibility. Intel power supplies such as the iSBC 645 Power Supply generate an AC Low signal (ACLO/), and a Memory Protect (MPRO/) signal for this purpose. The timing of these two signals is critical for implementing a battery back-up scheme. The MPRO/ signal is used by the RAM boards to prevent access to memory during a power-down condition. The ACLO/ signal is not used by the RAM boards, but could be used by the CPU board. Refer to the INTEL MULTIBUS SPECIFICATION for guidelines on battery back-up schemes.

Connector J1 is referenced in the INTEL iLBX BUS SPECIFICATION and the battery back-up signals are supported by the iSBC CX-Series boards. Connect the appropriate battery back-up, memory protect, and other control lines to the connector, as listed in Appendix A.

### PREPARATION FOR USE

NOTE

Data integrity is not guaranteed during an active memory access cycle in which a memory protect signal (MPRO/) is generated by the power supply.

When battery back-up power is to be installed for use with the RAM board, remove the following factory installed jumpers:

22 - 23

24 - 25

8Ø - 81

88 - 89

Battery backup power enters the board at J1-1 and J1-3 on the auxiliary connector. Ground is on J1-2 and J1-4. See Appendix A for connector J1 pin assignments.

Always remove both battery back-up and system power from the RAM boards before installing or removing the boards from a system cardcage. Failure to do so could result in damage to the boards.

### 2.5 BOARD INSTALLATION

The iSBC CX-Series RAM Boards are compatible with all MULTIBUS backplanes and cardcages. For iLBX bus compatibility, a special iLBX connector must be used to link the processor board to the memory board. The iLBX bus uses connector P2 and may not be compatible with earlier configurations of connector P2. Refer to Section 2.4.8 for battery backup information.

### 2.6 FACTORY DEFAULT JUMPERS

For each of the iSBC CX-Series boards, Table 2-13 provides a list of the jumpers that are installed at the factory. Figure 2-5 provides a jumper post location diagram of the boards.

### PREPARATION FOR USE

Table 2-13. Factory Installed Jumpers

| Jumper    | Function      | Ø28CX | Ø56CX | Ø12CX | Ø1ØCX | ø2øcx |

|-----------|---------------|-------|-------|-------|-------|-------|

|           |               |       |       |       |       |       |

| ØØ1 – ØØ2 | Refresh       | I     | Ι     | I     | Ι     | I     |

| ØØ5 – ØØ6 | Refresh       | I     | I     | r     | I     | Ι     |

| Ø1Ø – Ø11 | SPRQT         | I     | Ι     | I     | I     | Ι     |

| Ø13 – Ø14 | CAS Timing    | I     | Ι     | Ι     | Ι     | r     |

| Ø19 – Ø2Ø | R/C Timing    | I     | Ι     | I     | Ι     | Ι     |

| Ø22 – Ø23 | +5 <b>V</b> B | I     | Ι     | Ι     | Ι     | I     |

| Ø24 – Ø25 | +5 <b>V</b> B | I     | I     | I     | I     | I     |

| Ø26 – Ø3Ø | Board Size    | N     | I     | Ι     | I     | Ι     |

| Ø26 – Ø31 | Board Size    | I     | N     | N     | N     | N     |

| Ø27 – Ø32 | Board Size    | I     | I     | r     | I     | N     |

| Ø27 – Ø3Ø | Board Size    | N     | N     | N     | N     | I     |

| Ø28 – Ø33 | Board Size    | I     | I     | N     | N     | N     |

| Ø28 – Ø35 | Board Size    | N     | N     | I     | Ι     | I     |

| Ø29 – Ø34 | Deselect      | ı     | I     | Ι     | I     | I     |

| Ø39 – Ø55 | I/O Address   | I     | 1     | r     | Ι     | Ι     |

| Ø43 – Ø59 | iLBX ACK      | I     | I     | I     | I     | I     |

| Ø68 – Ø69 | iLBX ACK      | I     | Ι     | 1     | I     | I     |

| Ø7Ø – Ø76 | 1 MB Page     | ı     | I     | I     | I     | I     |

| Ø8Ø – Ø81 | +5VB          | I     | 1     | τ     | r     | r     |

| Ø83 – Ø84 | I/O Address   | I     | I     | Ι     | I     | I     |

| Ø86 – Ø87 | I/O Address   | Ι     | I     | Ι     | I     | I     |

| Ø88 – Ø89 | +5 <b>V</b> B | Ι     | Ι     | I     | Ι     | I     |

| Ø91 – Ø99 | ilbx BDSEL    | I     | r     | Ι     | Ι     | I     |

| 1Ø6 – 1Ø7 | ilbx BDSEL    | I     | I     | I     | I     | Ι     |

| 1Ø9 – 11Ø | ilbx BDSEL    | I     | Ι     | I     | I     | I     |

| 114 - 117 | Board Size    | I     | N     | N     | N     | N     |

| 155 - 117 | Board Size    | N     | N     | N     | I     | I     |

| 116 - 117 | Board Size    | N     | I     | I     | N     | N     |

| 118 - 12Ø | Board Size    | I     | Ι     | N     | Ι     | N     |

| 119 - 12Ø | Board Size    | N     | N     | N     | N     | I     |

| 12Ø - 121 | Board Size    | N     | N     | I     | N     | N     |

| 13Ø - 14Ø | INT Ø/        | I     | r     | I     | Ι     | I     |

| 145 - 146 | Test Only     | I     | I     | I     | I     | I     |

| 148 - 149 | ARBTR Time    | Ī     | I     | I     | I     | I     |

|           |               |       |       |       |       |       |

Notes: I = jumper installed; N = jumper not installed.

2-23

# CHAPTER 3 ECC OPERATION AND PROGRAMMING INFORMATION

### 3.1 INTRODUCTION

The iSBC CX-Series RAM boards each use two special registers to pass ECC mode control and status information to and from the system master iSBC board. These registers are called the Control Status Register (CSR) and the Error Status Register (ESR). This chapter describes the two registers, and explains how to program them for the desired operations. Board initialization procedures are given in Section 3.5.

### 3.2 MODES OF ECC OPERATION

There are six ECC modes of operation on this series of RAM boards. Each mode is obtained by software programming from the master iSBC board. The six modes are:

- a. Interrupt on any error mode;

- b. Interrupt on non-correctable error only mode;

- c. Correcting mode;

- d. Non-correcting mode;

- e. Diagnostic mode;

- f. Examine syndrome word mode.

Modes (a) and (b) can be used in conjunction with modes (c) and (d). The modes are described in the following sections. Mode programming information is provided in Section 3.3.

### 3.2.1 INTERRUPT ON ANY ERROR MODE

In this mode the RAM board will interrupt the iSBC processor board when any error (single-bit or multiple-bit) is detected by the ECC circuitry. Interrupts are discussed in Section 2.4.5.

#### 3.2.2 INTERRUPT ON NON-CORRECTABLE ERROR ONLY MODE

In this mode the RAM board will interrupt the iSBC processor board only when a non-correctable (multiple-bit) error is detected by the ECC circuitry. A multiple-bit error is not correctable by the ECC circuitry. Interrupts are discussed in Section 2.4.5.

### 3.2.3 CORRECTING MODE

In this mode the RAM board corrects any correctable error (single-bit error). Words which are not correctable are not modified. Interrupts are generated on any error only or on non-correctable errors only, depending on the mode selected. Interrupts are discussed in Section 2.4.5.

### 3.2.4 NON-CORRECTING MODE

In this mode the RAM board does not correct any error. The ECC circuitry continues to check for errors, but no corrective action is taken. Interrupts continue as described above. Interrupts are discussed in Section 2.4.5.

### 3.2.5 DIAGNOSTIC MODE

This mode is used for testing the on-board ECC circuitry. In this mode the Write Enable Strobe to the ECC RAM array is continuously disabled. The diagnostic mode can be used to simulate errors and in conjunction with the examine syndrome word mode to examine the check bits generated by the ECC circuitry. Refer to Section 4.3.3 for more Diagnostic Mode information.

### 3.2.6 EXAMINE SYNDROME WORD MODE

This mode, in conjunction with the diagnostic mode, is used for testing the ECC memory. In this mode, the syndrome bits (check bits) are clocked into the Error Status Register (ESR) on every memory read or write cycle. The ESR translation PROM (U155) switches to a transparent mode in the Examine Syndrome Word mode. This allows the actual syndrome word generated by the 8206 device to be examined. The six ESR bits are gated onto MULTIBUS data lines DAT0/ - DAT5/. Refer to Section 4.3.3 for more Examine Syndrome Word Mode information.

### 3.3 PROGRAMMING INFORMATION

The following five sections describe how to program the Control Status Register (CSR) and how to read the Error Status Register (ESR). The CSR and the ESR provide a means of controlling and viewing the status of ECC operations. These registers are accessed via the system master iSBC board's I/O port addresses. The CSR is written to by asserting IOWC/ to the MULTIBUS lines and the ESR is read by asserting IORC/. Because the CSR and the ESR occupy the same I/O port, the CSR may not be read. The ESR is cleared by a write to the board I/O address.

The ECC circuitry could malfunction if the CSR is loaded at the same time an iLBX bus memory access is taking place. In a single CPU system, this means that there must be no DMA activity on the iLBX bus while the CPU is loading the CSR. In a multiple CPU system, ensure that one CPU is not loading the CSR while another CPU board is accessing the memory board via the iLBX bus.

### 3.3.1 CONTROL STATUS REGISTER (CSR) PROGRAMMING

The CSR is an eight-bit register (on the RAM board) which is programmed by the processor to select one of several operating modes. To program the CSR, assert IOWC/ when the port address and data are stable on the MULTIBUS lines. CSR format is shown below; a summary of programming is given in Table 3-1; Table 3-2 provides a list of the most typical ECC modes, shown in hexadecimal format. The codes shown can be written directly to the CSR, during system initialization. Table 3-1 also gives the condition of the CSR after a RESET or POWER-UP condition.

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| В7. | В6 | В5 | В4 | В3 | В2 | В1 | ВØ  |

Table 3-1. RAM Board Control Status Register Format Summary

| Bit Ø | Interrupt on Correctable Error: When this bit is low (Ø), a MULTIBUS interrupt is asserted only on an uncorrectable error. When this bit is high (1), the RAM board asserts a MULTIBUS interrupt on any data error (single or multiple-bit).  POWER-UP & RESET CONDITION: HIGH (1)                                                                                                                                                                                                                                                                                    |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 1 | Diagnostic Mode Select. When this bit is high (1), the diagnostic mode is deselected. When low (0), the diagnostic mode is selected.  POWER-UP & RESET CONDITION: HIGH (1).                                                                                                                                                                                                                                                                                                                                                                                           |

| Bit 2 | Correct/Non-Correcting Modes: When this bit is high (1) every correctable error which occurs will be corrected by the on-board circuitry. The RAM board will continue to overwrite even if an uncorrectable error occurs during write-byte cycles. An overwrite should be performed to clear errors during memory initialization. When this bit is low (Ø) the board will not correct any errors. The RAM board will abort write-byte cycles if an uncorrectable error is detected on the read portion of the cycle. Refer to Section 4.3 for additional information. |

|       | POWER-UP & RESET CONDITION: HIGH (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Bit 3 | Examine Syndrome Word Mode: When this bit is high (1), the Examine Syndrome Word mode is deselected. When this bit is low (Ø), the Examine Syndrome Word mode is selected.  POWER-UP & RESET CONDITION: HIGH (1)                                                                                                                                                                                                                                                                                                                                                      |

| Bit 4 | Reserved: must be low (Ø).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Bit 5 | Reserved: must be low (Ø).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Bit 6 | Reserved: must be low (Ø).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Bit 7 | Reserved: must be low (Ø).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Table 3-2. Typical ECC Operating Modes (Hex)

| Hex Code | Mode Description                                    |  |  |  |  |  |

|----------|-----------------------------------------------------|--|--|--|--|--|

| ØF       | Correcting, Interrupt on Correctable Error.         |  |  |  |  |  |

| ØE       | Correcting, Interrupt on Non-Correctable Error.     |  |  |  |  |  |

| ØВ       | Non-correcting, Interrupt on Correctable Error.     |  |  |  |  |  |

| ØA       | Non-correcting, Interrupt on Non-Correctable Error. |  |  |  |  |  |

| ØØ       | Diagnostic mode, syndrome read selected.            |  |  |  |  |  |

### NOTE

Memory must be cleared after a RESET, and before starting system write or read operations. Refer to Section 3.5.

### 3.3.2 INTERRUPT ON ANY ERROR MODE PROGRAMMING

Bit  $\emptyset$  selects the interrupt mode. When bit  $\emptyset$  is high, the RAM board will issue an interrupt to the MULTIBUS when any error is detected.

### 3.3.3 INTERRUPT ON NON-CORRECTABLE ERROR ONLY MODE PROGRAMMING

Bit  $\emptyset$  selects the interrupt mode. When bit  $\emptyset$  is low, the RAM board will issue an interrupt to the MULTIBUS only when a non-correctable error is detected.

### 3.3.4 CORRECTING AND NON-CORRECTING MODE PROGRAMMING

Bit 2 selects the correcting mode when high, or the non-correcting mode when low.

### 3.3.5 DIAGNOSTIC MODE PROGRAMMING

Bit 1 deselects the diagnostic mode when high, or selects the diagnostic mode when low. This mode can be used for simulating errors in memory. The simulated errors should be detected by the ECC circuitry. In this mode the Write Enable strobe to the ECC RAM array is continuously inactive.

### 3.3.6 EXAMINE SYNDROME WORD MODE PROGRAMMING

Bit 3 deselects the examine syndrome word mode when high (1), or selects the examine syndrome word mode when low  $(\emptyset)$ . The examine syndrome word mode is used in conjunction with the diagnostic mode. This mode allows testing the check bit generation circuitry of the board. In this mode, the syndrome (check) bits are clocked into the error status register upon every read (or write) cycle. Refer to Section 4.3 for additional information on this mode.

Table 3-3. RAM Board Error Status Register Format

| <u>6 5</u>              | Meaning                               |  |  |

|-------------------------|---------------------------------------|--|--|

| ø ø                     | Error in row Ø                        |  |  |

| Ø 1<br>1 Ø              | 1<br>2                                |  |  |

| 1 1                     | 3                                     |  |  |

|                         |                                       |  |  |

| Bit<br><u>4 3 2 1 Ø</u> | Meaning                               |  |  |

| 43219                   | <u>neanting</u>                       |  |  |

| ø ø ø ø                 | Error in data bit Ø                   |  |  |

| Ø Ø Ø Ø 1               | 1                                     |  |  |

| Ø Ø Ø 1 Ø<br>Ø Ø Ø 1 1  | 2<br>3                                |  |  |