**FWD8006**

**MULTIBUS Compatible**

**Winchester/Floppy Controller**

**OEM Manual**

FWD8006

MULTIBUS Compatible

Winchester/Floppy Controller

OEM MANUAL

Document Number: 3000822

Revision: D

Date: May 15, 1984

APPLICABLE PRODUCT NUMBERS

PWB Assy: 0004352-0001

Prog Assy: 1002035-C001

Warning: This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. As temporarily permitted by regulation it has not been tested for compliance with the limits for Class A computing devices pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

The following are trademarks of Intel Corporation:

i Intel iSBC iSAX i48K Multibus and the combination of iSBC, iSAX, or i48K and a numerical suffix

## CONTENTS

|       |                                                  |          |

|-------|--------------------------------------------------|----------|

| I.    | CONTROLLER OVERVIEW                              | I - 1    |

| A.    | INTRODUCTION AND FEATURES                        | I - 1    |

| B.    | FWD8006 COMMAND and STATUS                       | I - 2    |

| C.    | FWD8006 DATA TRANSFER                            | I - 2    |

| D.    | FWD8006 ECC/CRC                                  | I - 3    |

| E.    | FUNCTIONAL SPECIFICATIONS                        | I - 4    |

| F.    | PHYSICAL SPECIFICATIONS                          | I - 6    |

| G.    | DISK FORMATS AND CAPACITIES                      | I - 7    |

| II.   | PREPARATION FOR USE                              | II - 1   |

| A.    | UNPACKING                                        | II - 1   |

| B.    | I/O ADDRESS and MEMORY WAKE-UP ADDRESS SELECTION | II - 1   |

| C.    | OPTION STRAPPING                                 | II - 4   |

| D.    | DRIVE STRAPPING                                  | II - 12  |

| E.    | DRIVE CABLE REQUIREMENTS                         | II - 16  |

| III.  | PROGRAMMING THE FWD8006                          | III - 1  |

| A.    | MULTIBUS ADDRESS GENERATION                      | III - 1  |

| B.    | PROGRAMMED I/O                                   | III - 4  |

| C.    | INTERRUPTS                                       | III - 6  |

| D.    | MEMORY BASED CONTROL PATHS                       | III - 7  |

| 1.    | WUB - Wake-up Block                              | III - 8  |

| 2.    | CCB - Channel Control Block                      | III - 9  |

| 3.    | CIB - Controller Invocation Block                | III - 10 |

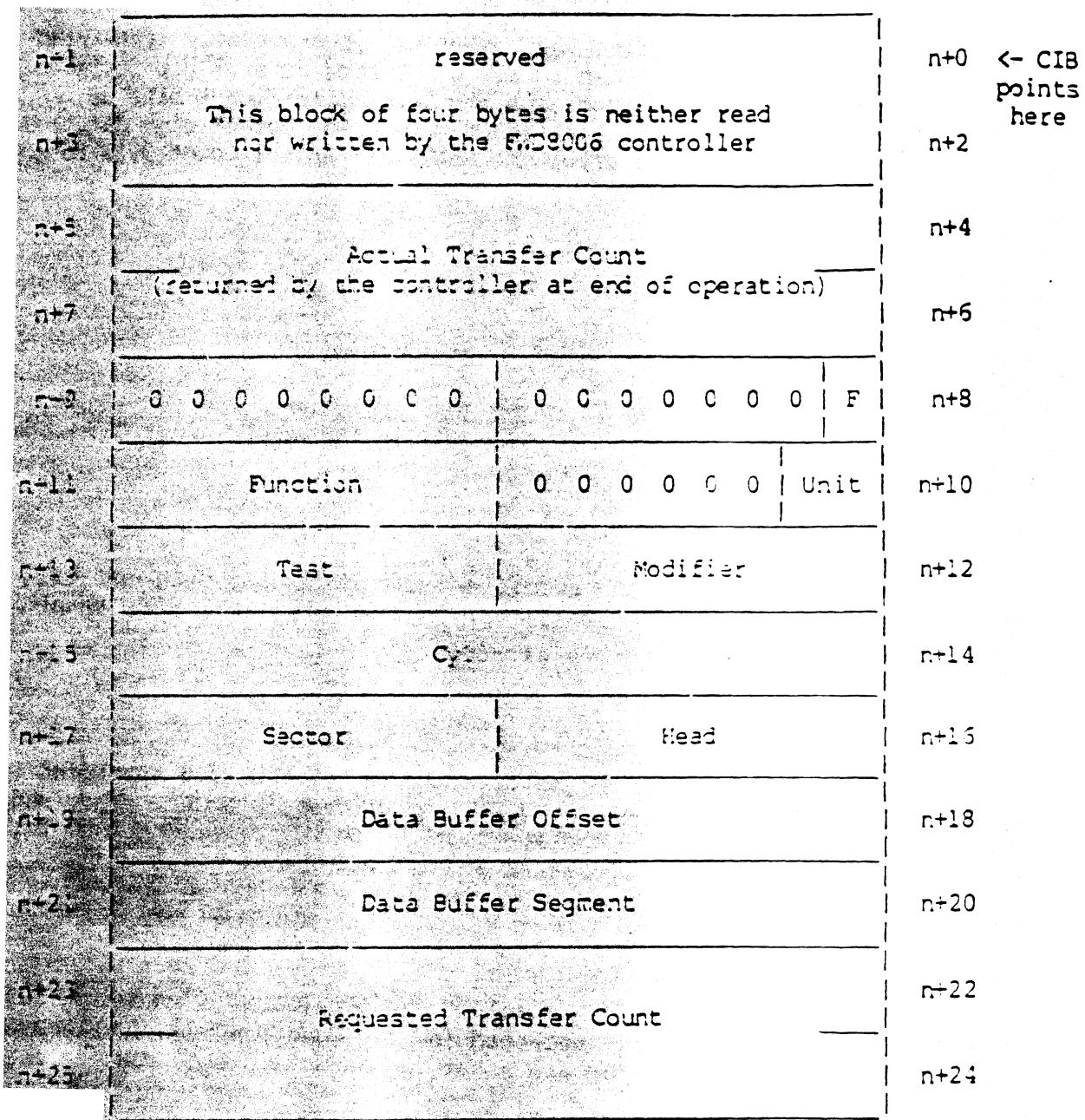

| 4.    | ICPB - Input / Output Parameter Block            | III - 12 |

| E.    | FWD8006 COMMANDS                                 | III - 16 |

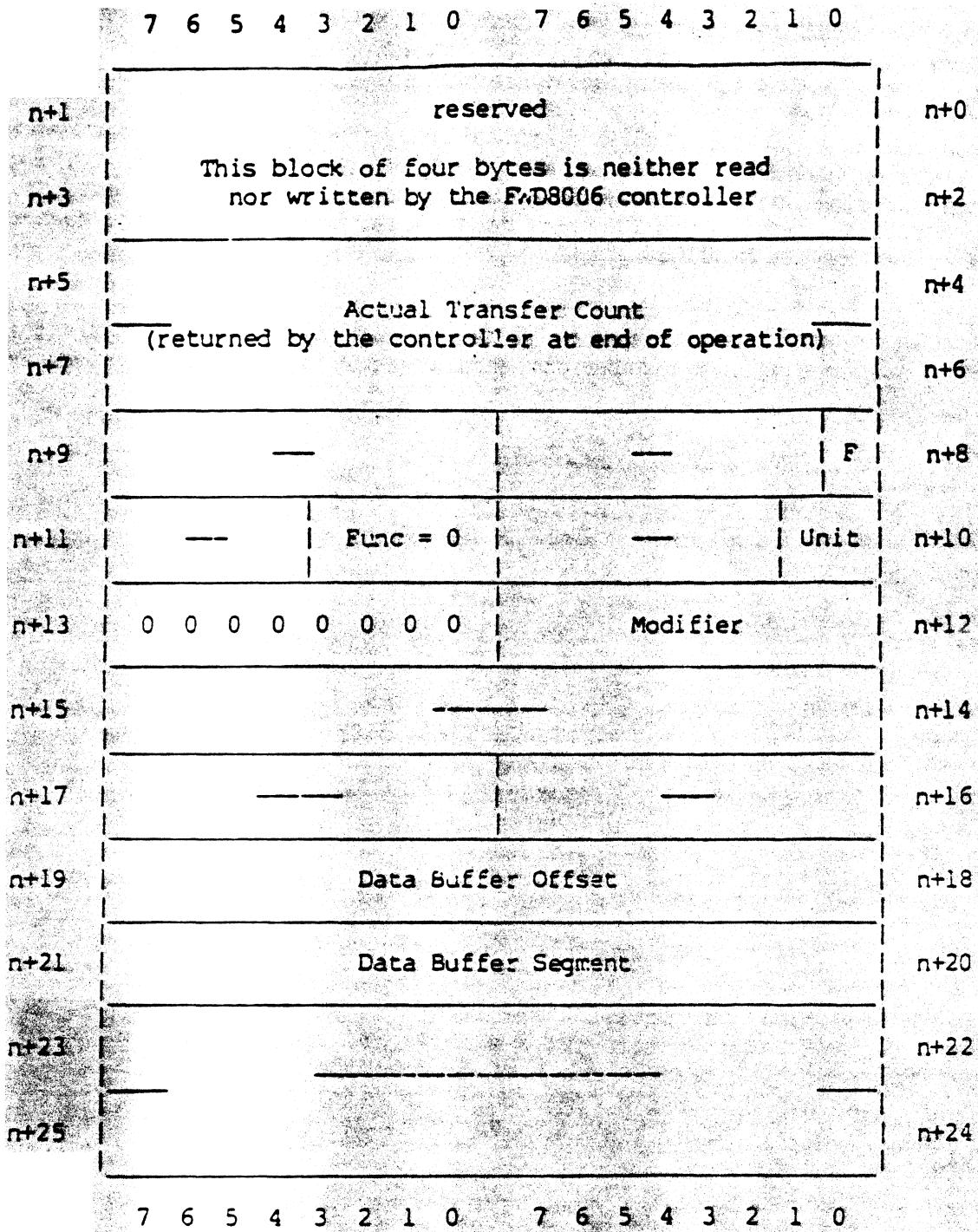

| 1.    | Initialize - Set Disk Drive Parameters           | III - 17 |

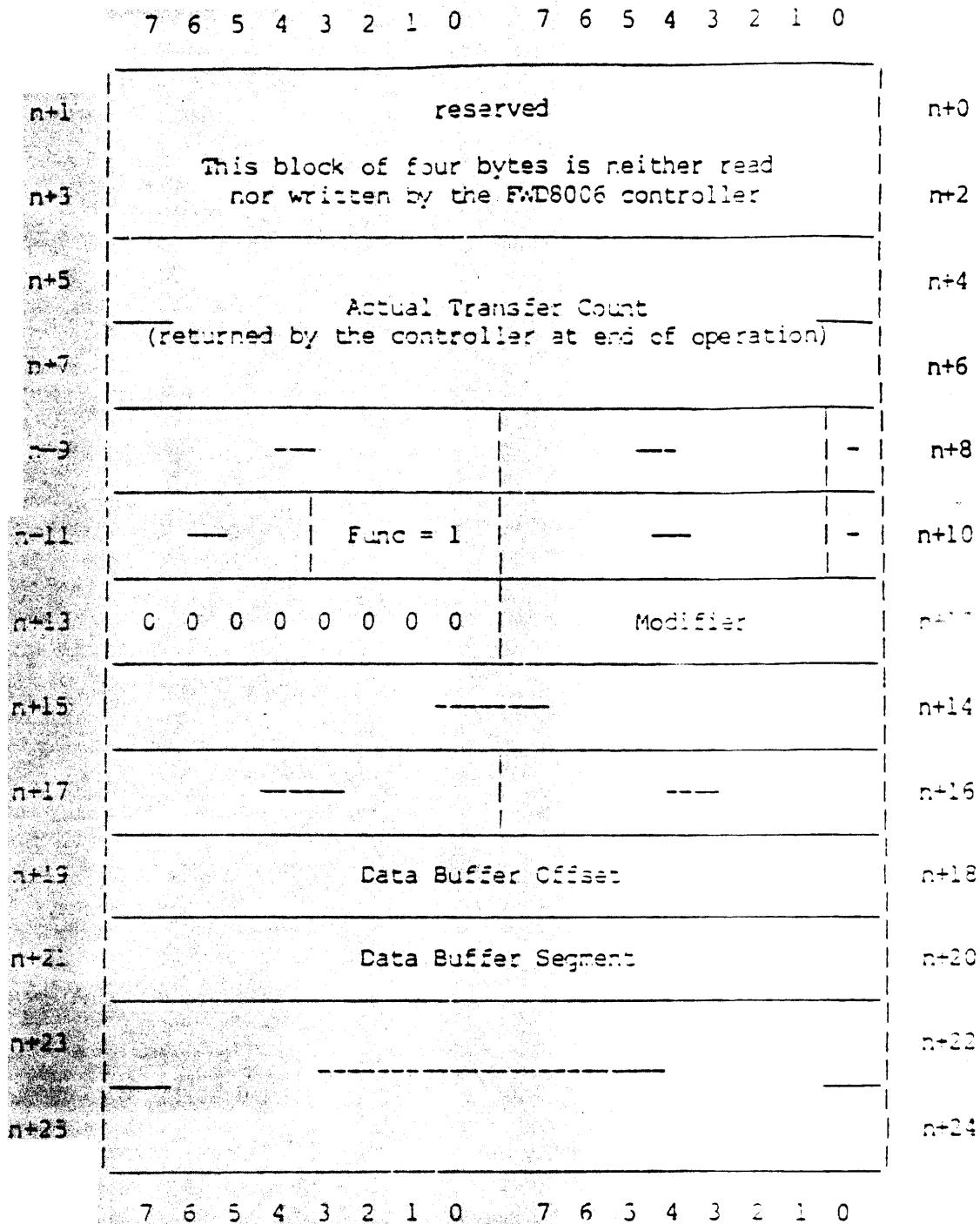

| 2.    | Transfer Status - Read Extended Status Buffer    | III - 21 |

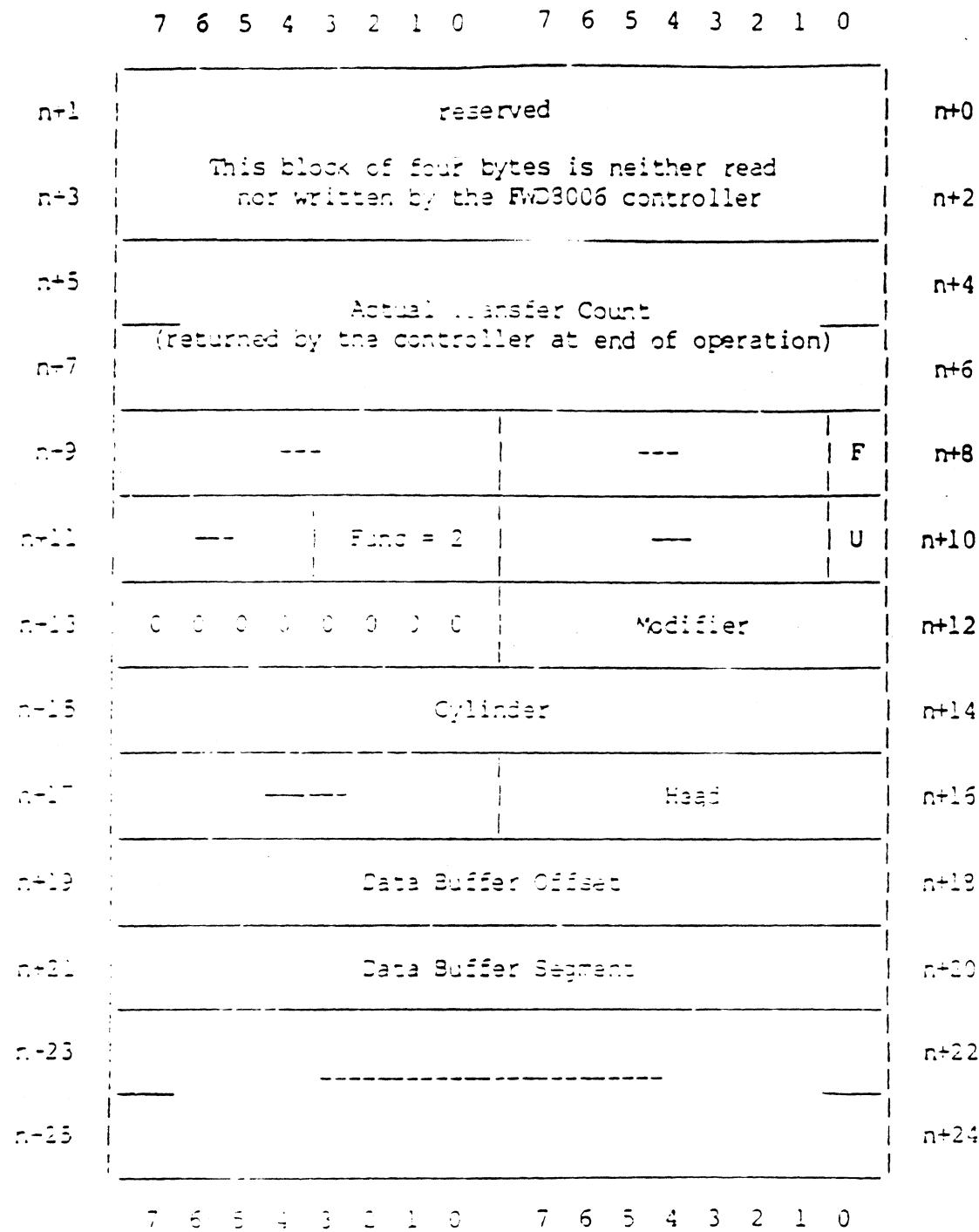

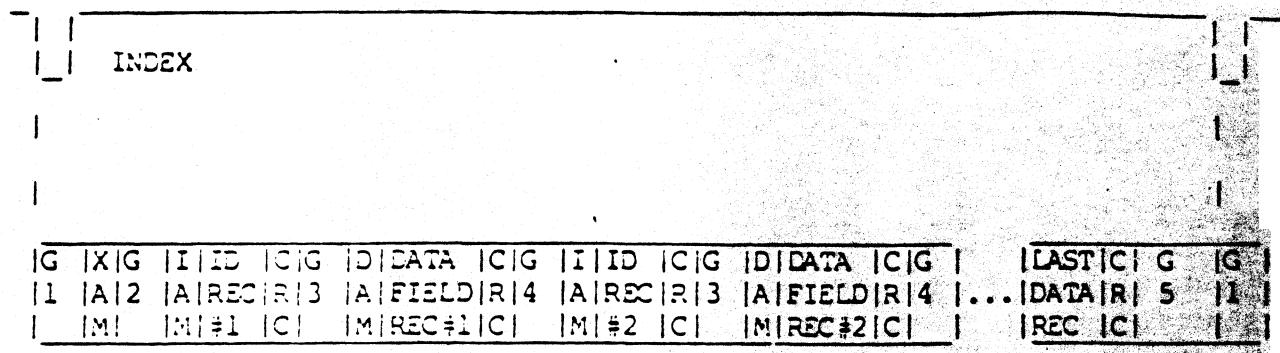

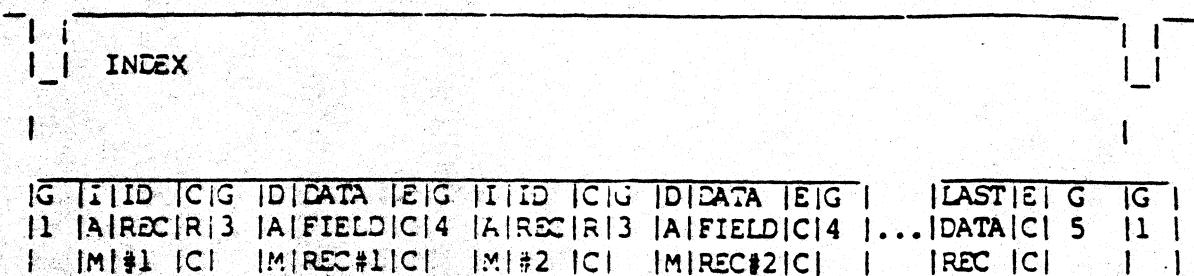

| 3.    | Format - Write Sector Data to a Disk Track       | III - 24 |

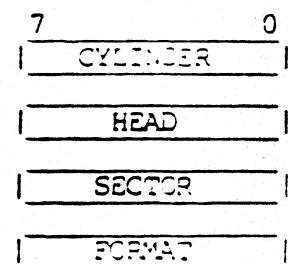

| 4.    | Read ID - Read Next Sector ID Field              | III - 27 |

| 5.    | Read Data - Read Disk Data Into Memory           | III - 29 |

| 6.    | Read Buffer - Read Disk Data Into Controller     | III - 31 |

| 7.    | Write Data - Write Memory Data onto Disk         | III - 33 |

| 8.    | Write Buffer - Write Controller Data onto Disk   | III - 35 |

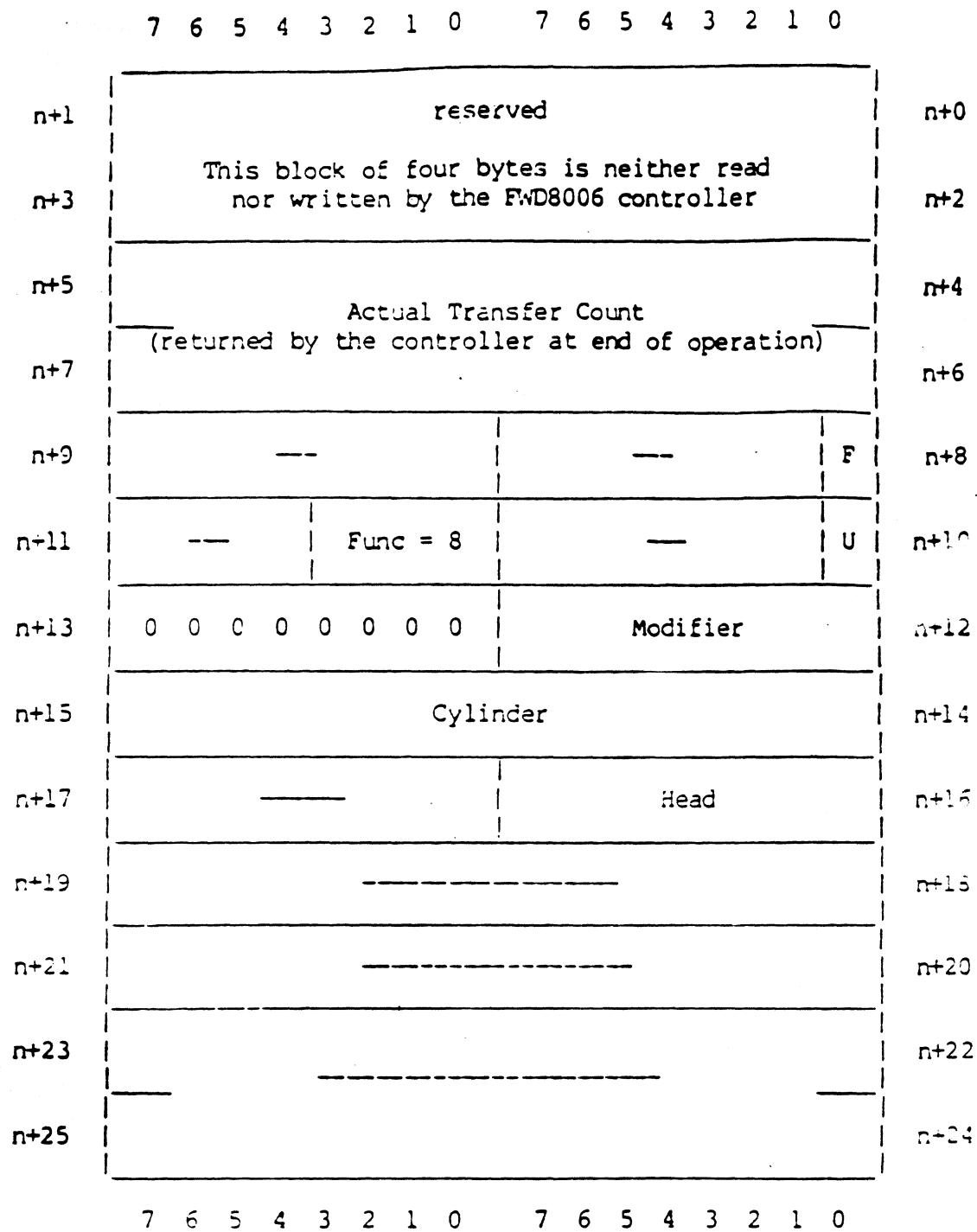

| 9.    | Seek - Initiate Drive Carriage Positioning       | III - 37 |

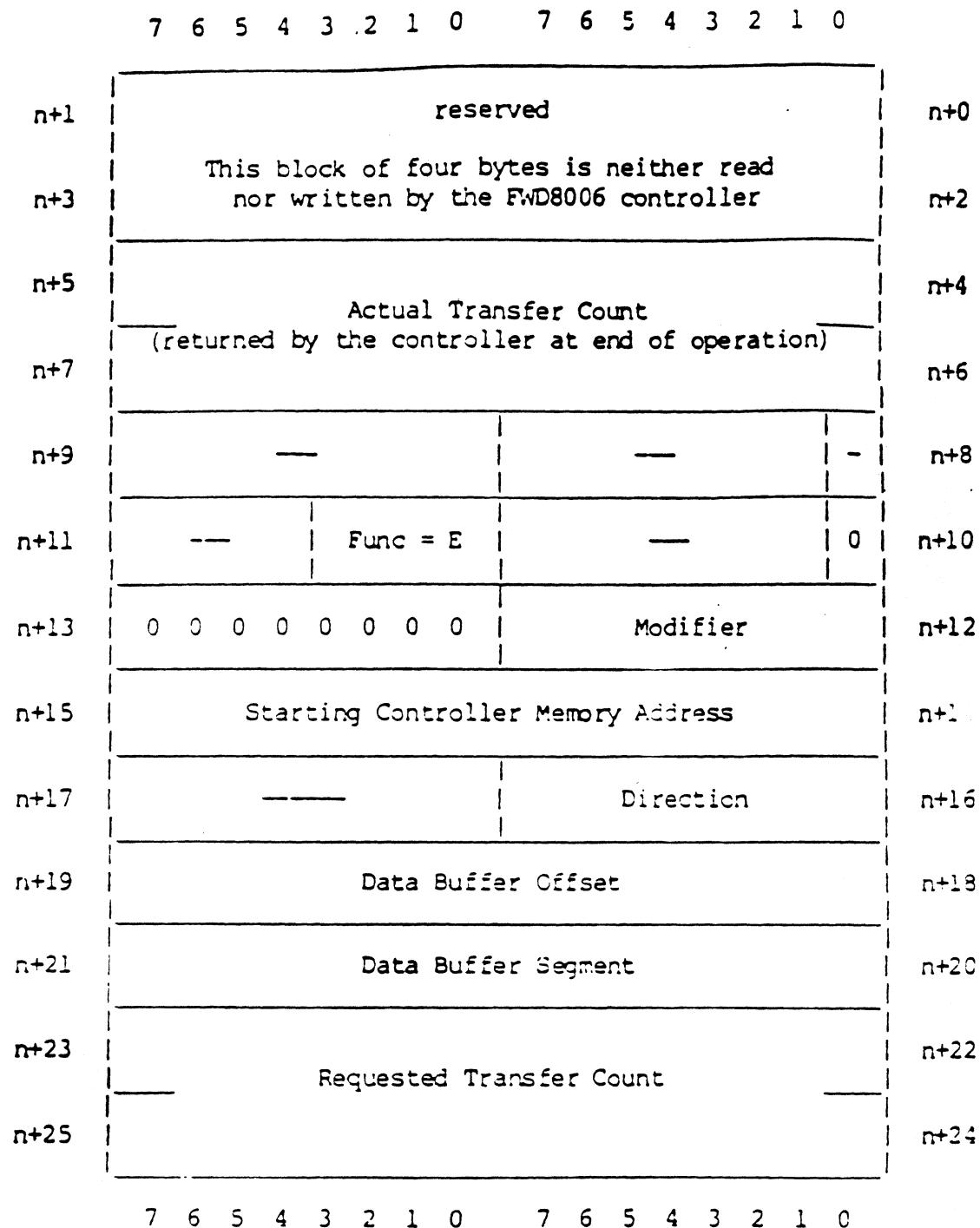

| 10.   | Buffer I/O - Transfer Controller/Memory Data     | III - 39 |

| 11.   | Diagnostic - Begin Fault Detection Diagnostic    | III - 41 |

| F.    | DATA TRANSFER CONTROL                            | III - 48 |

| Bit 6 | - Direct Winchester Disk/ Multibus Transfer      | III - 48 |

| Bit 5 | - Selective Word Wide Multibus Transfers         | III - 49 |

| Bit 2 | - Floppy Deleted Data Address Marks              | III - 49 |

| G.    | ISSUING COMMANDS and RECEIVING STATUS            | III - 51 |

| H.    | ERROR PROCESSING                                 | III - 53 |

| I.    | MEDIA FILE MANAGEMENT                            | III - 55 |

## FIGURES

|                |                                                |        |

|----------------|------------------------------------------------|--------|

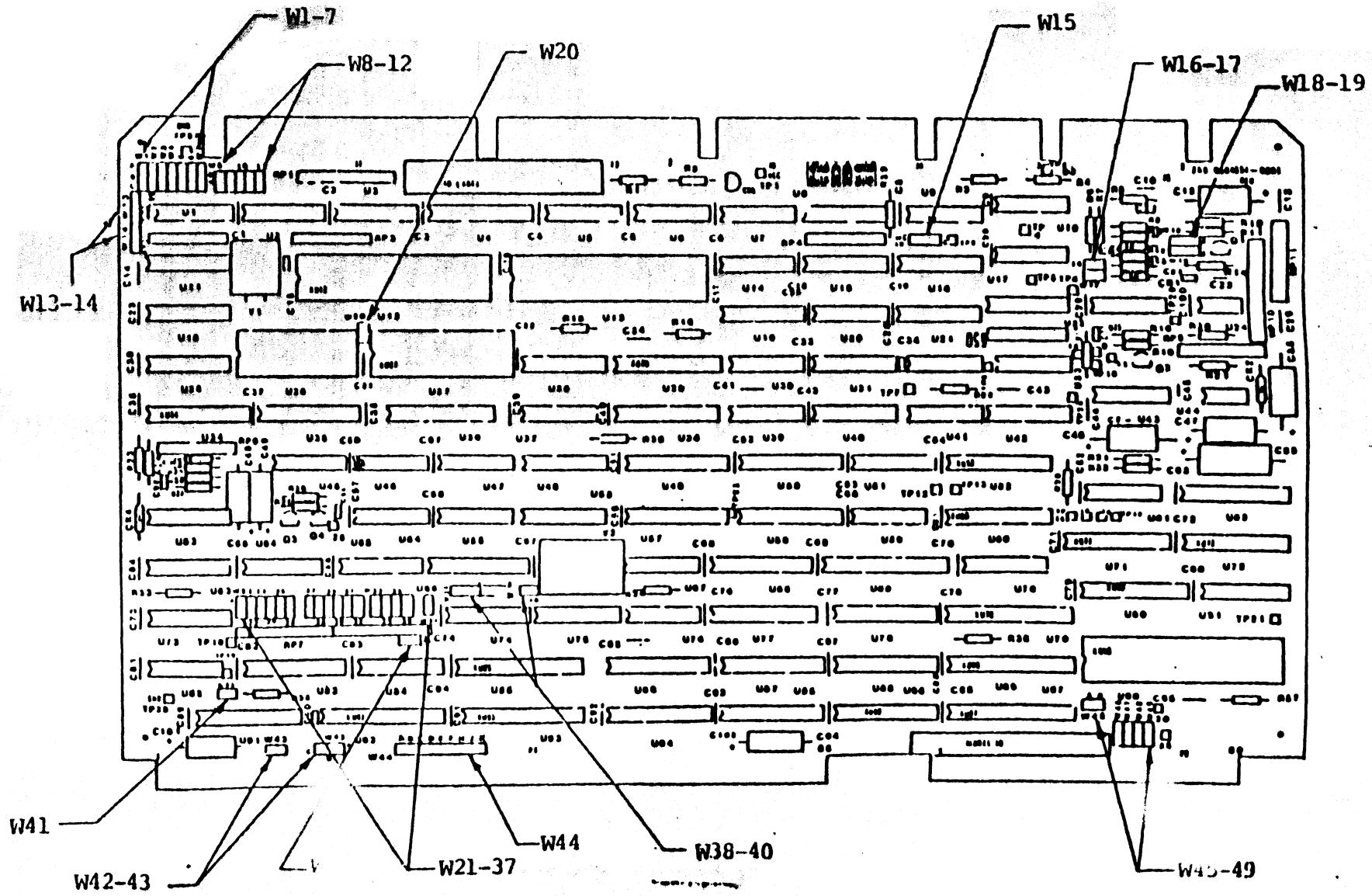

| Figure II-1.   | FWD8006 PWB - Jumper Locations .....           | II-11  |

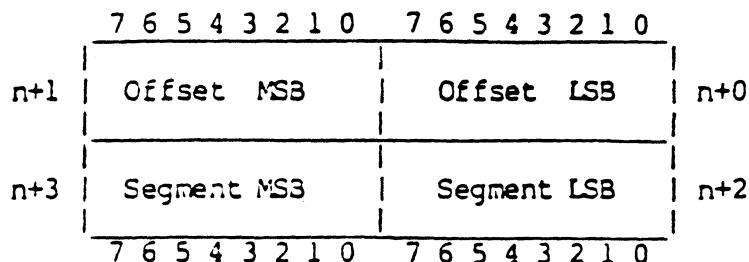

| Figure III-1.  | Segmented Address Format .....                 | III-2  |

| Figure III-2.  | Wake-Up Block .....                            | III-8  |

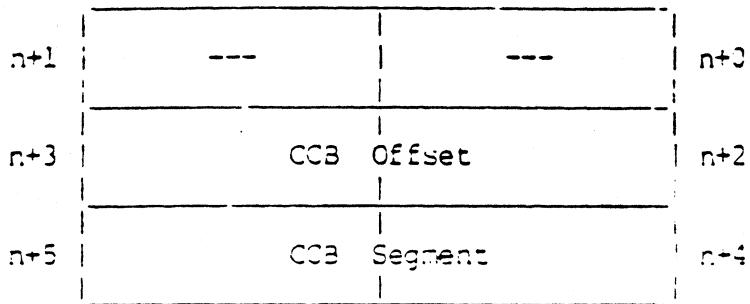

| Figure III-3.  | Channel Control Block .....                    | III-9  |

| Figure III-4.  | Channel Invocation Block .....                 | III-10 |

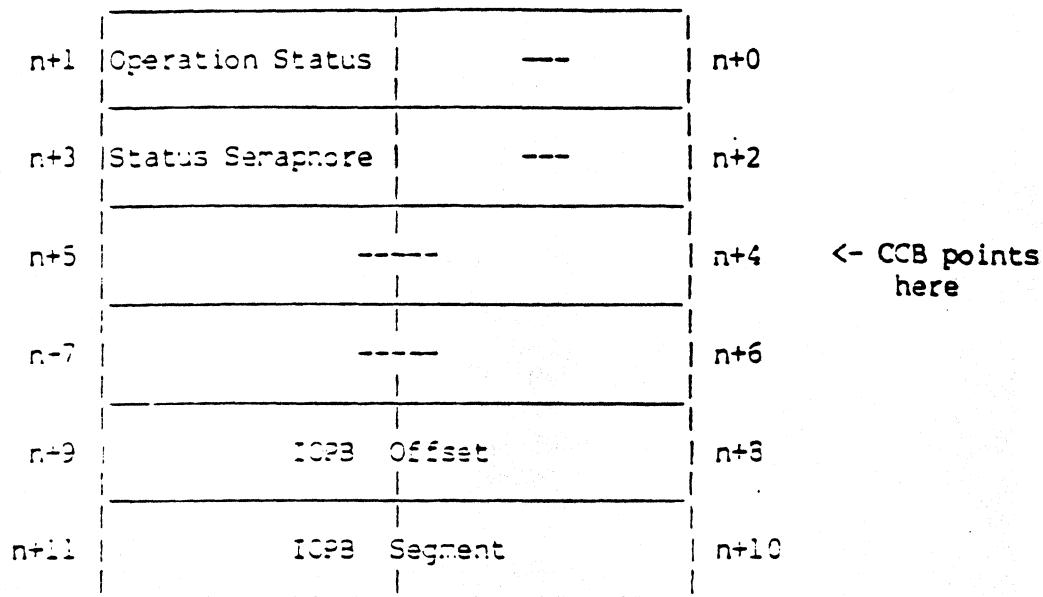

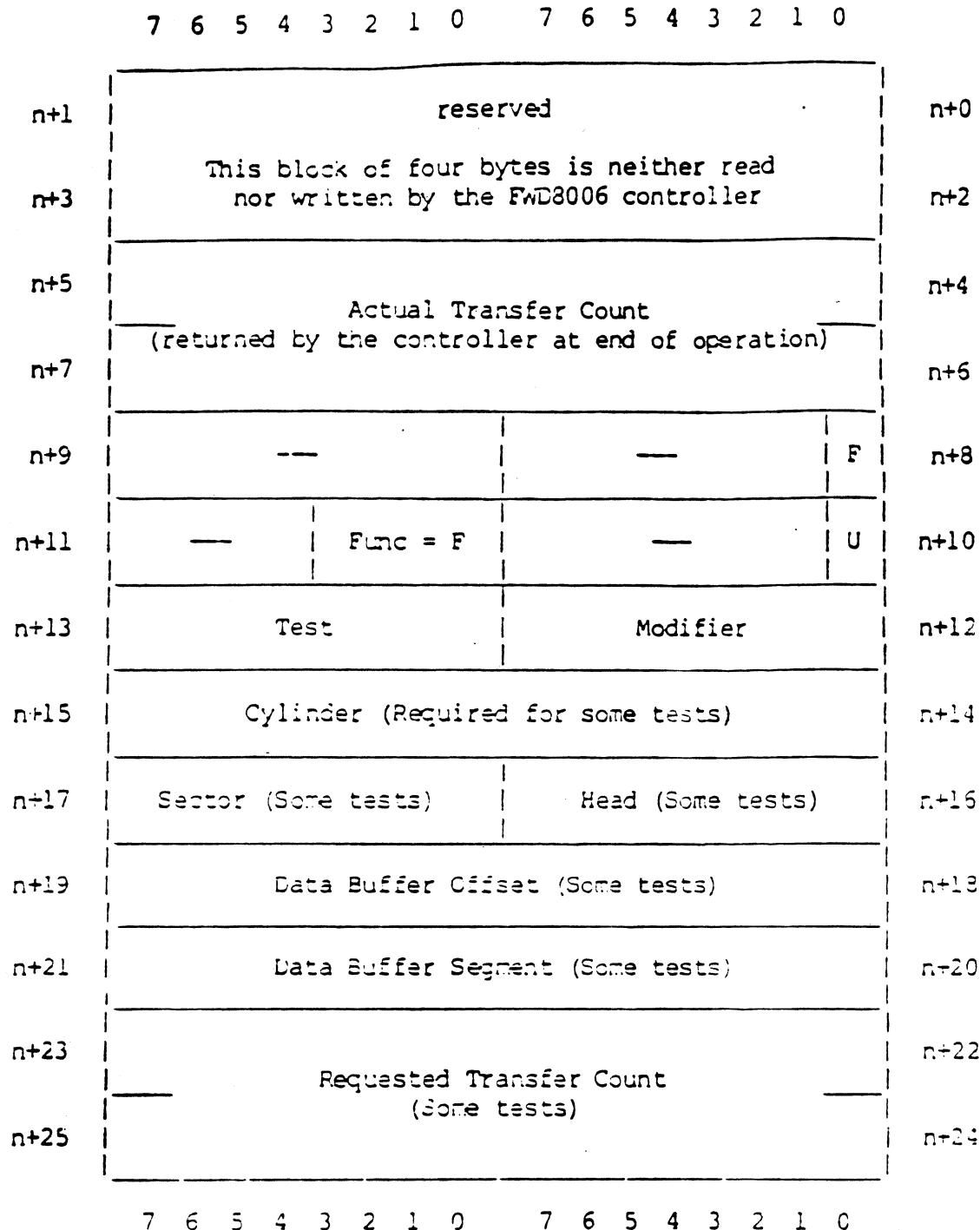

| Figure III-5.  | Typical I/O Parameter Block .....              | III-12 |

| Figure III-6.  | ICPB - Initialize Command .....                | III-17 |

| Figure III-7.  | ICPB Extension - Initialize Command .....      | III-18 |

| Figure III-8.  | ICPB - Transfer Status Command .....           | III-21 |

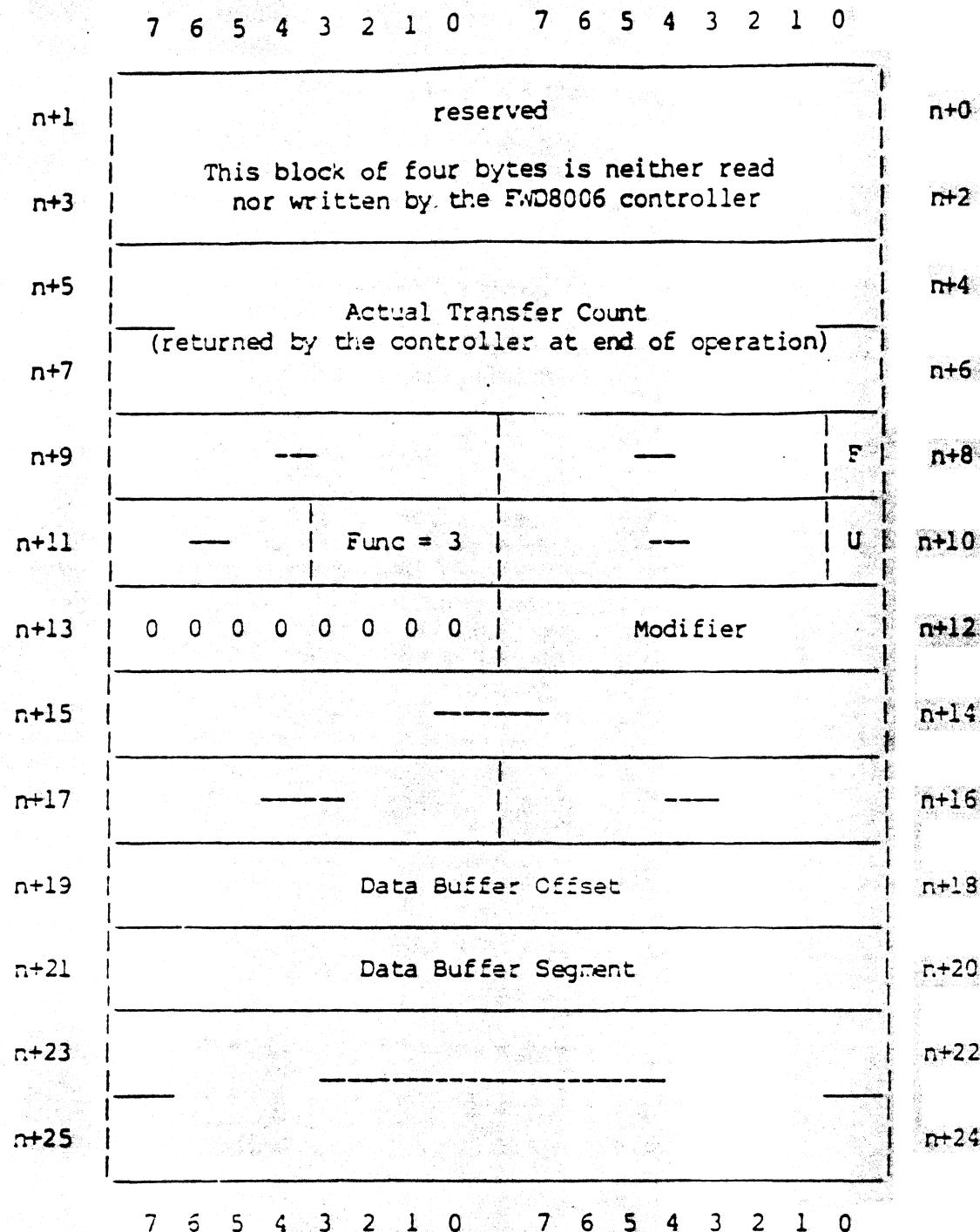

| Figure III-9.  | IOPB - Format Command .....                    | III-24 |

| Figure III-10. | ICPB Extension - Format Command .....          | III-25 |

| Figure III-11. | IOPB - Read Sector ID Command .....            | III-27 |

| Figure III-12. | Data Buffer - Read Sector ID Command .....     | III-28 |

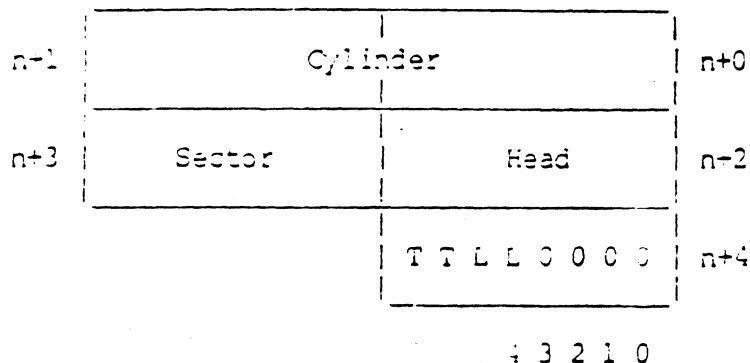

| Figure III-13. | ICPB - Read Data Command .....                 | III-29 |

| Figure III-14. | ICPB - Read to Buffer and Verify Command ..... | III-31 |

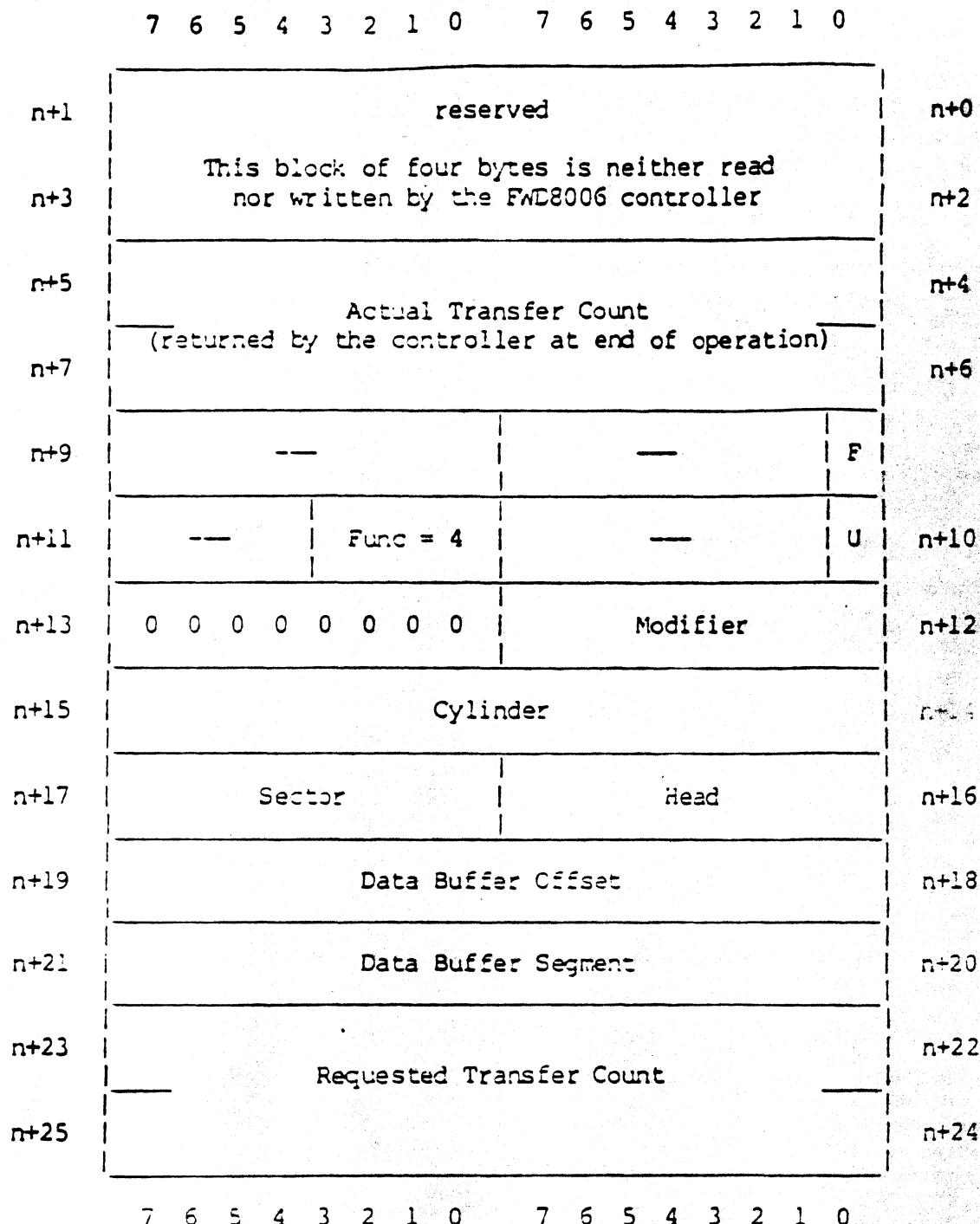

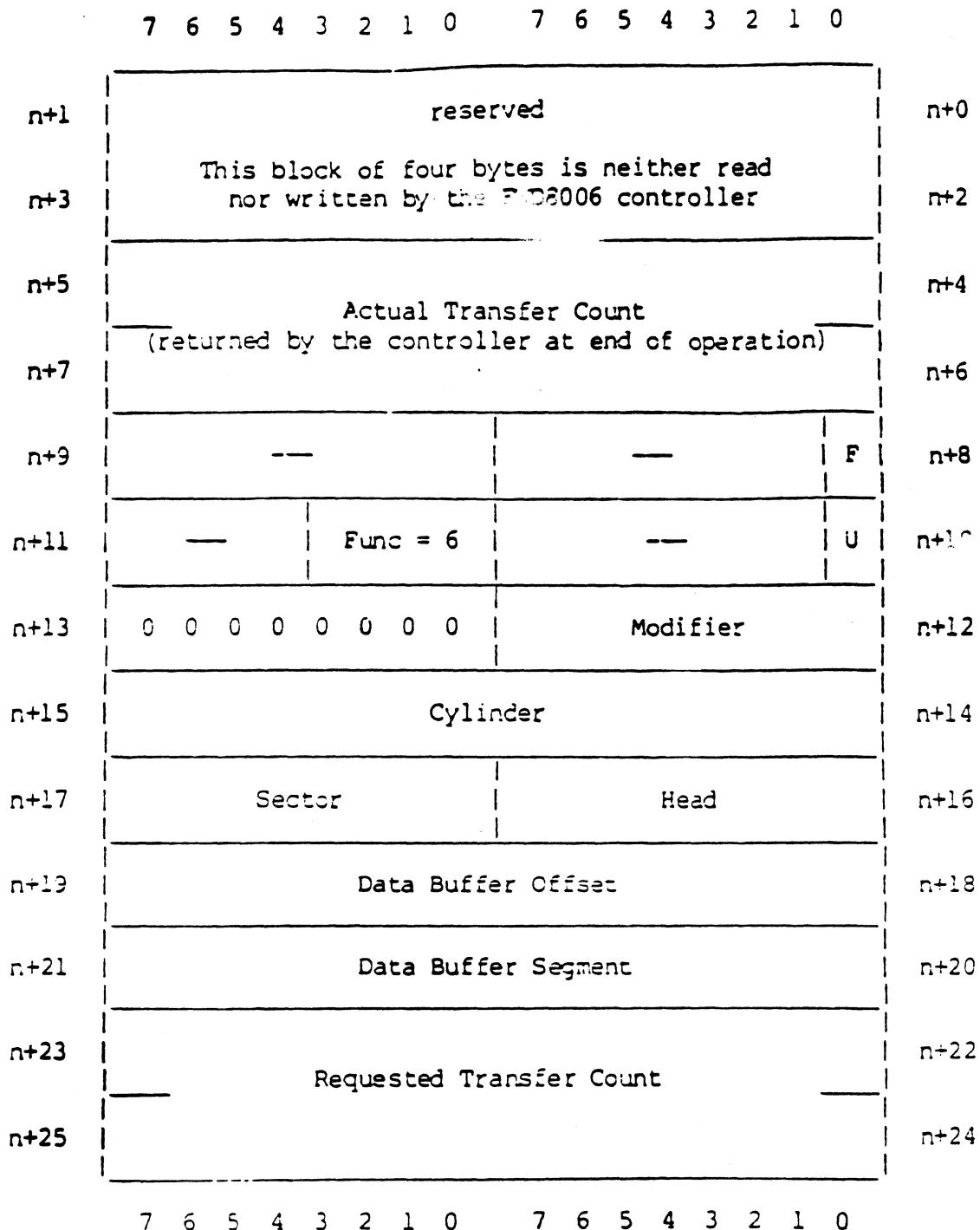

| Figure III-15. | IOPB - Write Data Command .....                | III-33 |

| Figure III-16. | ICPB - Write Buffer Data Command .....         | III-35 |

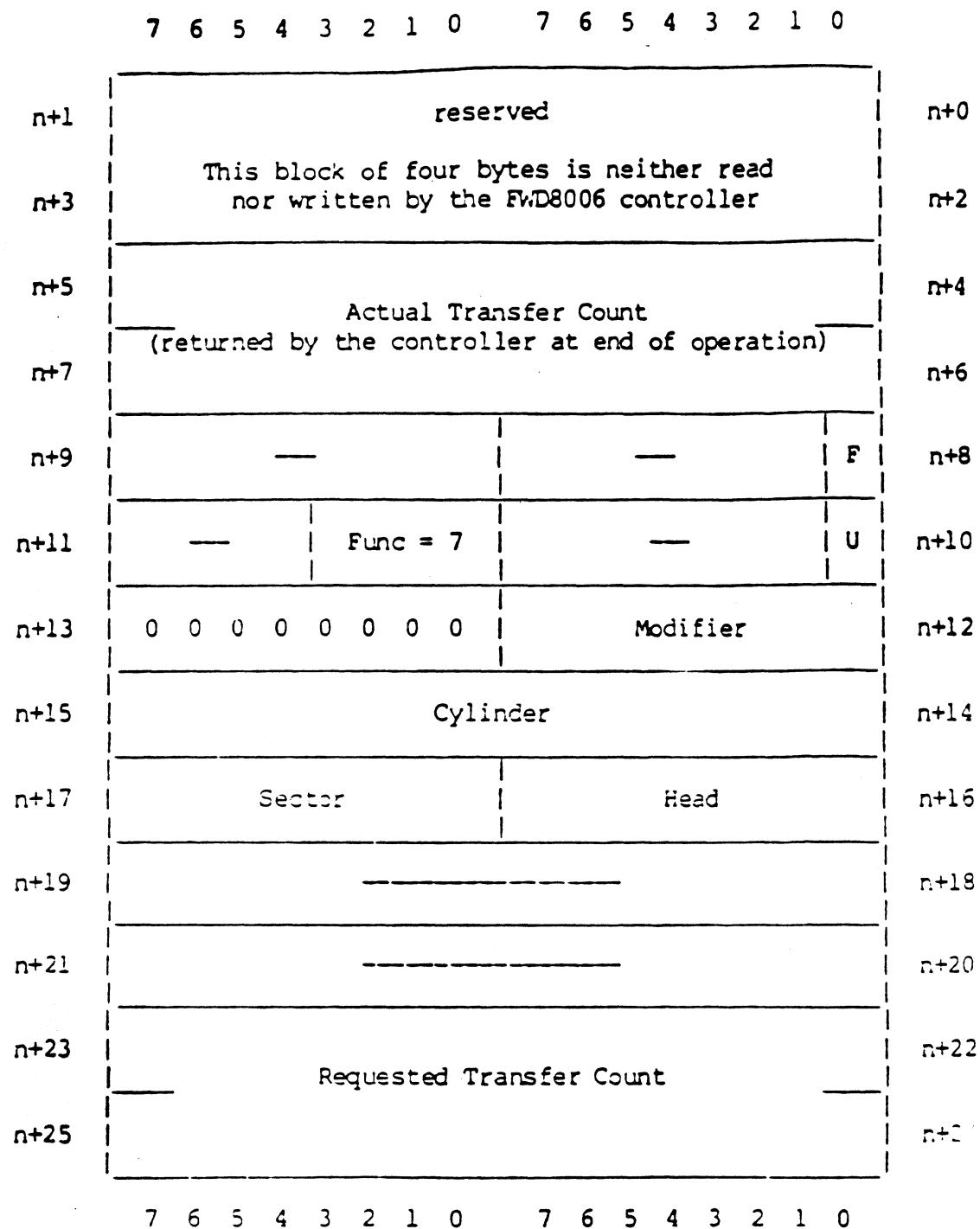

| Figure III-17. | IOPB - Initiate Track Seek Command .....       | III-37 |

| Figure III-18. | ICPB - Buffer I/O Command .....                |        |

| Figure III-19. | IOPB - Diagnostic Command .....                |        |

| Figure III-20. | ICPB Extension - Diagnostic Command .....      |        |

## TABLES

|             |                                                          |       |

|-------------|----------------------------------------------------------|-------|

| Table I-1.  | 8" Floppy Diskette Formats .....                         | I-7   |

| Table I-2.  | 5-1/4" Floppy Disk Format .....                          | I-8   |

| Table I-3.  | 5-1/4" Winchester Disk Formats .....                     | I-10  |

| Table I-4.  | 8" Floppy Drive Parameters .....                         | I-11  |

| Table I-5.  | 5-1/4" Floppy Drive Parameters .....                     | I-14  |

| Table I-6.  | 5-1/4" Winchester Drive Parameters .....                 | I-15  |

| Table I-7.  | 3-1/2" Floppy Drive Parameters .....                     | I-16  |

| Table I-8.  | 5-1/4" Winchester Drive Parameters .....                 | I-17  |

| Table I-9.  | Winchester Drive Compatibility .....                     | I-18  |

| Table II-1. | 8" Floppy Disk Drive Cable (50-Pin, J1) .....            | II-16 |

| Table II-2. | 5-1/4" Floppy Disk Drive Cable (34-Pin, J2) .....        | II-17 |

| Table II-3. | 5-1/4" Winchester Disk Drive Cable (34-Pin, J3) .....    | II-17 |

| Table II-4. | Winchester Differential Data Cable (20-Pin, J4/J5) ..... | II-17 |

| Table II-5. | Floppy Drive Options .....                               | II-17 |

| Table II-6. | Winchester Drive Options .....                           | II-15 |

CONTENTS (Cont.)

|     |                                           |        |

|-----|-------------------------------------------|--------|

| IV. | MEDIA ORGANIZATION.....                   | IV - 1 |

| A.  | PHYSICAL MEDIA ORGANIZATION .....         | IV - 1 |

| B.  | 8" FLOPPY DISK FORMAT .....               | IV - 3 |

| C.  | 5-1/4" AND 3-1/2" FLOPPY DISK FORMAT..... | IV - 4 |

| D.  | WINCHESTER DISK FORMAT .....              | IV - 5 |

| V.  | FAULT DETECTION and DIAGNOSTICS .....     | V - 1  |

| A.  | CONTROLLER SELF TEST .....                | V - 1  |

| B.  | SYSTEM and DRIVE TEST .....               | V - 2  |

| C.  | TROUBLESHOOTING GUIDELINES .....          | V - 3  |

Appendix A -- Detailed FWU8006 Event Codes ..... Appendix A - 1

## I. CONTROLLER OVERVIEW

### A. INTRODUCTION AND FEATURES

The FW8006 is a complete single board controller which allows the user to interface up to two 5-1/4" Winchester and two 8" floppy disk drives, two 5-1/4" Winchester and two 5-1/4" floppy disk drives or two 5-1/4" Winchester and two Sony 3-1/2" floppy disk drives\* to any Multibus compatible computer system. A unique controller architecture utilizing a multi-processor combination of high integration LSI components and high speed bipolar circuitry is used to eliminate additional boards, special cabling, etc., while providing high reliability and performance through careful conservative design, reduced component count, reduced interconnections, and reduced power consumption.

- o Fully replaces the three board controller system consisting of the Intel iSBC 215, the Intel iSBX 218, and the Shugart SA1200.

- o Software compatible with the iSBC 215 / iSBX 218 combination to allow plug in replacement without costly software handler or file system modifications.

- o Comprehensive self test and drive diagnostics on board.

- o Patented data recovery phase locked loop design.

- o Single PC board requires only a single slot in Multibus backplane.

- o Program selectable formats for floppy and Winchester disk.

- o Supports 8" diskette compatible with the following formats ... industry standard media interchangeability: IBM Diskette 1, IBM Diskette 2, IBM Diskette 2D, Intel SBC 202, and Intel single density floppy development systems and controllers.

- o Supports 5-1/4" diskette compatible with the following formats for interchangeability between various systems: Intel iRMX-35 single density, Intel iRMX-35 double density, DEC personal computer, and SMS' FDC507-M and FW30106 controllers.

- o Supports Sony 3-1/2" diskette compatible with FM and MFM formats.\*

- o Seek overlap.

- o Supports 8 or 16 bit data transfers on a buffer by buffer basis.

\* The connection to Sony drives is via the 50 pin edge connector J1 with a跳接 cable to re-route all the drive signals.

- o Supports 16 bit, 20 bit, or 24 bit (IEEE 796) memory addressing to allow access to up to 16 Megabytes of memory.

- o Supports either 8 bit or 16 bit I/O addressing.

- o Low Winchester disk error rate and high data integrity guaranteed through the implementation of error correction (ECC).

- o Programmable full sector buffering or direct transfer for both floppy and Winchester drives.

#### B. FWD8006 COMMAND and STATUS

Except for hardware Start, Stop, and Reset controls, all command and status information associated with the FWD8006 is communicated through Multibus memory based tables. This mechanism allows for detailed control of the disk system by the host CPU and for extensive status returns to the host with a minimum of hardware handshaking and hardware protocol. The CPU overhead required for disk operation is reduced while the level of data transfer flexibility and control is enhanced. The FWD8006 is an intelligent controller. It is capable of large block transfers across sector, track, and cylinder boundaries without host intervention. It incorporates extensive error processing facilities to improve data recovery and to relieve the host of error handling responsibilities except in the rare case of an unrecoverable error. And if the controller or disk drive system should fail, the FWD8006 contains extensive built in diagnostics to quickly isolate the fault to the controller or a drive for minimum repair time.

#### C. FWD8006 DATA TRANSFER

Both direct and buffered data transfer are supported by the FWD8006. For Winchester disk transfers where the data rate approaches the bandwidth of the host Multibus system, data transfers can be direct, by locking the Multibus during transfer time, or buffered through an on board full sector buffer. Floppy disk data transfers, on the other hand, occur at a low enough rate that bus access constraints are far less severe. This allows the FWD8006 to do direct disk to Multibus transfers on all floppy accesses without locking the Multibus. In addition, for systems with mixed memory capabilities such as occurs with the combination of the 16K bytes of byte-access-RAM on an iSBC 80/30 CPU board together with a byte/word access iSBC 032 memory board, for example, the FWD8006 allows the access width (byte or word) to be specified for each data buffer independently to take maximum advantage of the increased speed and reduced Multibus bandwidth requirements of word DMA transfers.

#### D. FWD8006 ECC/CRC

The IBM standard 16 bit CRC is used for error detection on all sector ID fields and floppy disk data fields. The error rate for these fields is lower than for Winchester data fields and the CRC facility provides an excellent error detection capability. Winchester disk data integrity is provided by a 32 bit computer generated error correcting code designed especially for the types of errors found on Winchester technology disks. This code will detect all bursts of 15 bits or less and will correct all bursts of 6 bits or less. This span was chosen to cover the majority of Winchester errors while minimizing the probability of miscorrection. All error correction codes, including the SMS code, have some probability of miscorrection. This occurs when a group of independent errors produce the same error residue as would have occurred with a certain correctable error. To prevent this situation, the FWD8006 saves the error residue from the first read, reads the sector again, and compares the residues before making a correction. This process virtually guarantees user data integrity. The price for this reliability is that two disk revolutions, rather than one, elapse whenever an error is encountered. This results in negligible performance loss.

## E. FUNCTIONAL SPECIFICATIONS

Maximum number of drives: Two 8" floppies + two 5-1/4" Winchesters or Two 5-1/4" floppies + two 5-1/4" Winchesters or Two Sony 3-1/2" floppies + two 5-1/4" Winchesters

8" floppy drives supported: Shugart SA810, SA860, SA850, Tandon TM848-1, TM848-2

5" diskette formats: 128, 256, 512, and 1024 byte sectors in IBM Diskette 1, Diskette 2, and Diskette 2D format.

128 byte sectors in Intel SBC 202 format.

5-1/4" floppy drives supported: Shugart SA400, SA450, SA410, SA460, SA455, SA465

Tandon TM100-3, TM100-4

Micro Peripherals MPI91, MPI92

TEAC FD-353, 55F

5-1/4" diskette formats: 128, 256, 512, and 1024 byte sectors in Intel iRMX-86 FM format.

256, 512, and 1024 byte sectors in Intel iRMX-86 MFM format.

512 byte sectors in IBM personal computer format.

512 byte sectors in DEC personal computer format.

128, 256, 512, and 1024 byte sectors in SMS FD0507-M MFM format.

128, 256, 512, and 1024 byte sectors in SMS FD0106 MFM format.

3-1/2" floppy drives supported: Sony QA-D30V

3-1/2" diskette formats: 128, 256, 512 byte sectors in FM format

256, 512, 1024 byte sectors in MFM format

5-1/4" Winchester drives supported: Seagate ST306, ST406, ST412, ST413 and compatible.

Winchester drive formats: MFM encoding with program selectable sector lengths of 128, 256, 512 or 1024 bytes.

Data transfer: Winchester disk transfers can be buffered or direct by locking the Multibus. Floppy disk transfers can also be buffered or direct without locking the Multibus. Multibus transfer cycles can be either byte or word wide on a buffer by buffer basis.

**I/O address selection:**

Defined by hardware strapping. Slip-jumpers select either 8 bit I/O addressing or 16 bit addressing for full Multibus addressing range compatibility.

**Interrupt level selection:**

Defined by hardware strapping. Wire-wrap jumper selects one of 8 standard Multibus parallel interrupt request lines.

## PHYSICAL SPECIFICATIONS

Environmental:      Relative humidity: 10% to 90%

Operating temperature\*: 0 to 50 degrees C.

Storage temperature: -65 to 70 degrees C

\*Extreme temperatures may require forced air cooling,

i.e. 50 degrees C ambient requires 150 linear

feet/minute over component side of PC board in a

typical card cage application.

Electrical:      Operating voltage: 5V (5% tolerance)

Ripple and noise must not exceed 100 mV P-P.

Operating current:

0.2A (maximum)

Power is supplied by the host computer via the

standard Multibus EIO pins of connector P1.

Mechanical:      The controller PC board conforms to Multibus board

form factors as detailed in the IEEE 796 Bus

Specification.

## C. DISK FORMATS AND FILES

Table I-1. 8" FLOPPY DISKETTE FORMATS

| <u>Format</u> | <u>Density</u> | <u>Code</u> | <u>Byte/Sect</u> | <u>Sect/Trk</u> | <u>Sides</u> | <u>Cyl</u> | <u>Bytes/Diskette</u> |

|---------------|----------------|-------------|------------------|-----------------|--------------|------------|-----------------------|

| IBM 1 *       | Single         | FM          | 128              | 26              | 1            | 77         | 256,256               |

|               |                |             | 256              | 15              |              |            | 295,680               |

|               |                |             | 512              | 8               |              |            | 315,392               |

|               |                |             | 1024             | 4               |              |            | 315,392               |

| IBM 2 *       |                |             | 128              | 26              | 2            | 77         | 512,512               |

|               |                |             | 256              | 15              |              |            | 591,360               |

|               |                |             | 512              | 8               |              |            | 630,784               |

|               |                |             | 1024             | 4               |              |            | 630,784               |

| Double        | MFM            |             | 128              | 44              | 1            | 77         | 433,664               |

|               |                |             | 256              | 26              |              |            | 512,512               |

|               |                |             | 512              | 15              |              |            | 591,360               |

|               |                |             | 512              | 16              |              |            | 630,784               |

|               |                |             | 1024             | 8               |              |            | 630,784               |

| IBM 2D *      |                |             | 128              | 44              | 2            | 77         | 867,328               |

|               |                |             | 256              | 26              |              |            | 1,025,024             |

|               |                |             | 512              | 15              |              |            | 1,182,720             |

|               |                |             | 512              | 16              |              |            | 1,261,568             |

| IBM 2D *      |                |             | 1024             | 8               |              |            | 1,261,568             |

|               |                |             |                  |                 |              |            |                       |

| SSC 202       | Double         | MFM         | 128              | 52              | 1            | 77         | 512,512               |

Formats marked \* are fully compatible with the indicated IBM format.

Formats listed without \* are logical extensions of IBM formats.

The 202 format is fully compatible with the Intel SSC 202 double density floppy disk controller.

Table I-2. 5-1/4" FLOPPY DISKETTE FORMATS

| <u>Format</u> | <u>Density</u> | <u>Code</u> | <u>Byte/Sect</u> | <u>Sect/Trk</u> | <u>Sides</u> | <u>Cyl</u> | <u>Bytes/Diskette</u> |

|---------------|----------------|-------------|------------------|-----------------|--------------|------------|-----------------------|

| FD0507-M      | Double         | MFM         | 128              | 30              | 1            | 35         | 134,400               |

|               |                |             | 256              | 18              | 1            | 35         | 161,280               |

|               |                |             | 512              | 10              | 1            | 35         | 179,200               |

|               |                |             | 1024             | 5               | 1            | 35         | 179,200               |

|               |                |             | 128              | 30              | 1            | 40         | 153,600               |

|               |                |             | 256              | 18              | 1            | 40         | 184,320               |

|               |                |             | 512              | 10              | 1            | 40         | 204,800               |

|               |                |             | 1024             | 5               | 1            | 40         | 204,800               |

|               |                |             | 128              | 30              | 1            | 80         | 307,200               |

|               |                |             | 256              | 18              | 1            | 80         | 368,640               |

|               |                |             | 512              | 10              | 1            | 80         | 409,600               |

|               |                |             | 1024             | 5               | 1            | 80         | 409,600               |

|               |                |             | 128              | 30              | 2            | 35         | 268,800               |

|               |                |             | 256              | 18              | 2            | 35         | 322,560               |

|               |                |             | 512              | 10              | 2            | 35         | 358,400               |

|               |                |             | 1024             | 5               | 2            | 35         | 358,400               |

|               |                |             | 128              | 30              | 2            | 40         | 307,200               |

|               |                |             | 256              | 18              | 2            | 40         | 368,640               |

|               |                |             | 512              | 10              | 2            | 40         | 409,600               |

|               |                |             | 1024             | 5               | 2            | 40         | 409,600               |

|               |                |             | 128              | 30              | 2            | 80         | 614,400               |

|               |                |             | 256              | 18              | 2            | 80         | 737,280               |

|               |                |             | 512              | 10              | 2            | 80         | 819,200               |

|               |                |             | 1024             | 5               | 2            | 80         | 819,200               |

| FD05106       | Double         | MFM         | 128              | 26              | 1            | 80         | 256,240               |

|               |                |             | 256              | 16              | 1            | 80         | 327,680               |

|               |                |             | 512              | 10              | 1            | 80         | 409,600               |

|               |                |             | 1024             | 5               | 1            | 80         | 409,600               |

|               |                |             | 128              | 26              | 2            | 80         | 532,480               |

|               |                |             | 256              | 16              | 2            | 80         | 655,360               |

|               |                |             | 512              | 10              | 2            | 80         | 819,200               |

|               |                |             | 1024             | 5               | 2            | 80         | 819,200               |

Table I-1 1/4" FLOPPY DISKETTE FORMATS (continued)

| <u>Format</u>  | <u>Density</u> | <u>Code</u> | <u>Byte/Sect</u> | <u>Sect/Trk</u> | <u>Sides</u> | <u>Cyl</u> | <u>Bytes/Diskette</u> |

|----------------|----------------|-------------|------------------|-----------------|--------------|------------|-----------------------|

| iRMX-86 Single | FM             | 128         | 16               | 1               | 35           | 71,680     |                       |

|                |                | 256         | 9                | 1               | 35           | 80,640     |                       |

|                |                | 512         | 4                | 1               | 35           | 71,680     |                       |

|                |                | 1024        | 2                | 1               | 35           | 71,680     |                       |

|                |                | 128         | 16               | 2               | 35           | 143,360    |                       |

|                |                | 256         | 9                | 2               | 35           | 161,280    |                       |

|                |                | 512         | 4                | 2               | 35           | 143,360    |                       |

|                |                | 1024        | 2                | 2               | 35           | 143,360    |                       |

|                |                | 128         | 16               | 1               | 80           | 163,840    |                       |

|                |                | 256         | 9                | 1               | 80           | 184,320    |                       |

|                |                | 512         | 4                | 1               | 80           | 163,840    |                       |

|                |                | 1024        | 2                | 1               | 80           | 163,840    |                       |

|                |                | 128         | 16               | 2               | 80           | 327,680    |                       |

|                |                | 256         | 9                | 2               | 80           | 368,640    |                       |

|                |                | 512         | 4                | 2               | 80           | 327,680    |                       |

|                |                | 1024        | 2                | 2               | 80           | 327,680    |                       |

|                | Double         | FM          | 256              | 16              | 1            | 35         | 143,360               |

|                |                |             | 512              | 8               | 1            | 35         | 143,360               |

|                |                |             | 1024             | 4               | 1            | 35         | 143,360               |

|                |                | 256         | 16               | 2               | 35           | 286,720    |                       |

|                |                | 512         | 8                | 2               | 35           | 286,720    |                       |

|                |                | 1024        | 4                | 2               | 35           | 286,720    |                       |

|                |                | 256         | 16               | 1               | 80           | 327,680    |                       |

|                |                | 512         | 8                | 1               | 80           | 327,680    |                       |

|                |                | 1024        | 4                | 1               | 80           | 327,680    |                       |

|                |                | 256         | 16               | 2               | 80           | 655,360    |                       |

|                |                | 512         | 8                | 2               | 80           | 655,360    |                       |

|                |                | 1024        | 4                | 2               | 80           | 655,360    |                       |

| IBM PC         | Double         | FM          | 512              | 8               | 1            | 40         | 163,840               |

|                |                |             | 512              | 8               | 2            | 40         | 327,680               |

| IBM PC         | Double         | FM          | 512              | 9               | 1            | 40         | 184,320               |

|                |                |             | 512              | 9               | 2            | 40         | 368,640               |

| DEC PC         | Double         | FM          | 512              | 10              | 1            | 80         | 409,600               |

3000azzz

Table I-3. 3-1/2" FLOPPY DISKETTE FORMATS

| <u>Format</u> | <u>Density</u> | <u>Code</u> | <u>Byte/Sect</u> | <u>Sect/Trk</u> | <u>Sides</u> | <u>Cyl</u> | <u>Bytes/Diskette</u> |

|---------------|----------------|-------------|------------------|-----------------|--------------|------------|-----------------------|

| <b>Sony</b>   | <b>Single</b>  | <b>FM</b>   | 128              | 15              | 1            | 70         | 134,400               |

|               |                |             | 256              | 9               | 1            | 70         | 161,280               |

|               |                |             | 512              | 4               | 1            | 70         | 143,360               |

| <b>Double</b> | <b>MFH</b>     | <b>MFH</b>  | 256              | 15              | 1            | 70         | 268,800               |

|               |                |             | 512              | 9               | 1            | 70         | 322,560               |

|               |                |             | 1024             | 4               | 1            | 70         | 286,720               |

Table I-4. 5-1/4" WINCHESTER DISK FORMATS

| <u>Vendor</u> | <u>Model</u> | <u>Byte/Sect</u> | <u>Sect/Trk</u> | <u>Heads</u> | <u>Cyl</u> | <u>Formatted Capacity (MB)</u> |

|---------------|--------------|------------------|-----------------|--------------|------------|--------------------------------|

| Seagate       | ST506        | 128              | 54              | 4            | 153        | 4.230                          |

|               |              | 256              | 31              |              |            | 4.857                          |

|               |              | 512              | 17              |              |            | 5.327                          |

|               |              | 1024             | 9               |              |            | 5.640                          |

|               | ST406        | 128              | 54              | 2            | 306        | 4.230                          |

|               |              | 256              | 31              |              |            | 4.857                          |

|               |              | 512              | 17              |              |            | 5.327                          |

|               |              | 1024             | 9               |              |            | 5.640                          |

|               | ST412        | 128              | 54              | 4            | 306        | 8.460                          |

|               |              | 256              | 31              |              |            | 9.714                          |

|               |              | 512              | 17              |              |            | 10.654                         |

|               |              | 1024             | 9               |              |            | 11.280                         |

|               | ST419        | 128              | 54              | 6            | 306        | 12.690                         |

|               |              | 256              | 31              |              |            | 14.570                         |

|               |              | 512              | 17              |              |            | 15.981                         |

|               |              | 1024             | 9               |              |            | 16.921                         |

| Atasi         | 3033         | 128              |                 | 5            | 645        | 22.291                         |

|               |              | 256              | 31              |              |            | 25.594                         |

|               |              | 512              | 17              |              |            | 28.070                         |

|               |              | 1024             | 9               |              |            | 29.722                         |

|               | 3046         | 128              | 54              | 7            | 645        | 31.208                         |

|               |              | 256              | 31              |              |            | 35.831                         |

|               |              | 512              | 17              |              |            | 39.299                         |

|               |              | 1024             | 9               |              |            | 41.610                         |

| Maxtor        | XT-1065      | 128              | 54              | 7            | 918        | 44.417                         |

|               |              | 256              | 31              |              |            | 50.997                         |

|               |              | 512              | 17              |              |            | 55.932                         |

|               |              | 1024             | 9               |              |            | 59.222                         |

|               | XT-1105      | 128              | 54              | 11           | 918        | 69.797                         |

|               |              | 256              | 31              |              |            | 80.138                         |

|               |              | 512              | 17              |              |            | 87.893                         |

|               |              | 1024             | 9               |              |            | 93.063                         |

|               | XT-1140      | 128              | 54              | 15           | 918        | 95.178                         |

|               |              | 256              | 31              |              |            | 109.279                        |

|               |              | 512              | 17              |              |            | 119.854                        |

|               |              | 1024             | 9               |              |            | 126.904                        |

Table I-4. 5 1/4" WINCHESTER DISK FORMAT (continued)

| <u>Vendor</u> | <u>Model</u> | <u>Byte/Sect</u> | <u>Sect/Trk</u> | <u>Heads</u> | <u>Cyl</u> | <u>Formatted Capacity (MB)</u> |

|---------------|--------------|------------------|-----------------|--------------|------------|--------------------------------|

| Rodime        | 0204         | 128              | 54              | 8            | 320        | 17.695                         |

|               |              | 256              | 31              |              |            | 20.316                         |

|               |              | 512              | 17              |              |            | 22.282                         |

|               |              | 1024             | 9               |              |            | 23.593                         |

| Rodime        | 0208         | 128              | 54              | 8            | 640        | 35.389                         |

|               |              | 256              | 31              |              |            | 40.632                         |

|               |              | 512              | 17              |              |            | 44.564                         |

|               |              | 1024             | 9               |              |            | 47.186                         |

| Vertex        | V130         | 128              | 54              | 3            | 987        | 20.466                         |

|               |              | 256              | 31              |              |            | 23.498                         |

|               |              | 512              | 17              |              |            | 25.772                         |

|               |              | 1024             | 9               |              |            | 27.288                         |

|               | V150         | 128              | 54              | 5            | 987        | 34.110                         |

|               |              | 256              | 31              |              |            | 39.164                         |

|               |              | 512              | 17              |              |            | 42.954                         |

|               |              | 1024             | 9               |              |            | 45.481                         |

|               | V170         | 128              | 54              | 7            | 987        | 47.755                         |

|               |              | 256              | 31              |              |            | 54.830                         |

|               |              | 512              | 17              |              |            | 60.136                         |

|               |              | 1024             | 9               |              |            | 63.673                         |

| Tandon        | TM703        | 128              | 54              | 5            | 600        | 20.736                         |

|               |              | 256              | 31              |              |            | 23.808                         |

|               |              | 512              | 17              |              |            | 26.112                         |

|               |              | 1024             | 9               |              |            | 27.648                         |

| CMI           | CM6426       | 128              | 54              | 4            | 640        | 17.635                         |

|               |              | 256              | 31              |              |            | 20.316                         |

|               |              | 512              | 17              |              |            | 22.282                         |

|               |              | 1024             | 9               |              |            | 23.593                         |

|               | CM6640       | 128              | 54              | 6            | 640        | 26.542                         |

|               |              | 256              | 31              |              |            | 30.474                         |

|               |              | 512              | 17              |              |            | 33.423                         |

|               |              | 1024             | 9               |              |            | 35.389                         |

Table I-4. 5 1/4" WINCHESTER DISK FORMAT (continued)

| <u>Vendor</u> | <u>Model</u> | <u>Byte/Sect</u> | <u>Sect/Trk</u> | <u>Heads</u> | <u>Cyl</u> | <u>Formatted Capacity (MB)</u> |

|---------------|--------------|------------------|-----------------|--------------|------------|--------------------------------|

| Evotek        | ET5530       | 128              | 54              | 6            | 375        | 15.552                         |

|               |              | 256              | 31              |              |            | 17.856                         |

|               |              | 512              | 17              |              |            | 19.584                         |

|               |              | 1024             | 9               |              |            | 20.736                         |

|               | ET5540       | 128              | 54              | 8            | 375        | 20.736                         |

|               |              | 256              | 31              |              |            | 23.808                         |

|               |              | 512              | 17              |              |            | 26.112                         |

|               |              | 1024             | 9               |              |            | 27.648                         |

| Quantum       | Q520         | 128              | 54              | 4            | 512        | 14.155                         |

|               |              | 256              | 31              |              |            | 16.253                         |

|               |              | 512              | 17              |              |            | 17.826                         |

|               |              | 1024             | 9               |              |            | 18.874                         |

|               | Q540         | 128              | 54              | 8            | 512        | 28.311                         |

|               |              | 256              | 31              |              |            | 32.506                         |

|               |              | 512              | 17              |              |            | 35.651                         |

|               |              | 1024             | 9               |              |            | 37.748                         |

Note: Refer to section IV for detailed description of disk formats. Refer to Table I-9 for compatibility.

Table I-5. 8" FLOPPY DRIVE PARAMETERS

| Drive Model | Unformatted Capacity (MB) | Cyl | Sides | Rotational Latency (ms) | Avg Access Time (ms) | Step Time (ms) | Settling Time (ms) |

|-------------|---------------------------|-----|-------|-------------------------|----------------------|----------------|--------------------|

| SA810       | 0.40 S [1]<br>0.80 D      | 77  | 1     | 83.33                   | 89                   | 3              | 16                 |

| SA860       | 0.80 S<br>1.60 D          | 77  | 2     | 83.33                   | 89                   | 3              | 16                 |

| TM848-1     | 0.40 S<br>0.80 D          | 77  | 1     | 83.33                   | 91                   | 4              | 15                 |

| TM848-2     | 0.80 S<br>1.60 D          | 77  | 2     | 83.33                   | 91                   | 4              | 15                 |

| TM848-2E    | 0.80 S<br>1.60 D          | 77  | 2     | 83.33                   | 89                   | 3              | 16                 |

| M2896-63    | 0.80 S<br>1.60 D          | 77  | 2     | 83.33                   | 89                   | 3              | 16                 |

| SA850       | 0.80 S<br>1.60 D          | 77  | 2     | 83.33                   | 91                   | 3              | 15                 |

| SA800       | 0.80 S<br>1.60 D          | 77  | 1     | 83.33                   | 91                   | 8              | 8                  |

[1] S = single density; D = double density.

[2] Max data transfer rate is 31.25 KBytes/second for single density and 62.50 Kbytes/second for double density.

[3] Average data transfer rate based on 256 bytes/sector without interleave is 23 KBytes/second for single density and 40 KBytes/second for double density. A 2:1 interleave would cut average transfer rate by two.

-6. 5-1/4" FLOPPY DRIVE PARAMETERS

| <u>Drive Model</u> | <u>Unformatted Capacity (Kb)</u> | <u>Cyl</u> | <u>Sides</u> | <u>Rotational Latency (ms)</u> | <u>Avg Access Time (ms)</u> | <u>Step Time (ms)</u> | <u>Settling Time (ms)</u> |

|--------------------|----------------------------------|------------|--------------|--------------------------------|-----------------------------|-----------------------|---------------------------|

| SA400              | 109.4 S [1]                      | 35         | 1            | 100                            | 463                         | 40                    | 10                        |

| SA450              | 218.8 S<br>437.5 D               | 35         | 2            | 100                            | 298                         | 25                    | 15                        |

| SA410              | 250.0 S<br>500.0 D               | 80         | 1            | 100                            | 158                         | 6                     | 15                        |

| SA460              | 500.0 S<br>1000.0 D              | 80         | 2            | 100                            | 158                         | 6                     | 15                        |

| MP101              | 250.0 S<br>500.0 D               | 80         | 1            | 100                            | 133                         | 5                     | 15                        |

| MP102              | 500.0 S<br>1000.0 D              | 80         | 2            | 100                            | 133                         | 5                     | 15                        |

| TM100-3            | 250.0 S<br>500.0 D               | 80         | 1            | 100                            | 90                          | 5                     | 15                        |

| TM100-4            | 500.0 S<br>1000.0 D              | 80         | 2            | 100                            | 90                          | 5                     | 15                        |

| SD-553             | 250.0 S                          | 40         | 2            | 100                            | 93                          | 6                     | 15                        |

| SA455              | 500.0 D                          |            |              |                                |                             |                       |                           |

| SD-557             | 500.0 S<br>1000.0 D              | 80         | 2            | 100                            | 94                          | 6                     | 15                        |

| SA465              | 500.0 S<br>1000.0 D              | 80         | 2            | 100                            | 94                          | 3                     | 15                        |

[1] S = single density; D = double density.

[2] Max data transfer rate is 15.63 Kbytes/second for single density and 31.25 Kbytes/second for double density.

[3] Average data transfer rate based on 256 bytes/sector without interleave is 11.5 Kbytes/second for single density and 20.0 Kbytes/second for double density. A 2:1 interleave would cut average transfer rate by two.

3000822D

Table I-7. 3-1/2" FLOPPY DRIVE PARAMETERS

| Drive Model | Unformatted Capacity (MB) | Cyl | Sides | Rotational Latency (ms) | Avg Access Time (ms) | Step Time (ms) | Settling Time (ms) |

|-------------|---------------------------|-----|-------|-------------------------|----------------------|----------------|--------------------|

| QA-D33V     | 250.0 S [1] 500.0 D       | 80  | 2     | 100.0 ms                | 350                  | 12             | 30                 |

[1] S = single density; D = double density.

[2] Max data transfer rate is 31.25 Kbytes/second for single density and 62.50 Kbytes/second for double density.

[3] Average data transfer rate based on 256 bytes/sector without interleave is 23 KBytes/second for single density and 38 KBytes/second for double density. A 2:1 interleave would cut average transfer rate by two.

Table -3. 5-1/4" WINCHESTER DRIVE PARAMETERS

| Drive Model | Unformatted   |     |       | Rotational Latency (ms) | Avg Access Time (ms) | Data XFR Rate |      |

|-------------|---------------|-----|-------|-------------------------|----------------------|---------------|------|

|             | Capacity (MB) | Cyl | Heads |                         |                      | Max.          | Avg. |

| ST506       | 6.38          | 153 | 4     | 8.33                    | 85                   | 625           | 476  |

| ST406       | 6.38          | 306 | 2     | 8.33                    |                      | 625           | 476  |

| ST412       | 12.76         | 306 | 4     | 8.33                    | 85                   | 625           | 476  |

| ST419       | 19.14         | 306 | 6     | 8.33                    |                      | 625           | 476  |

3000822D

The FWDS006 controller supports all the Winchester drives listed in Table I-8 and compatibles. Table I-9 provides an easy reference for the 5-1/4" Winchester drive compatibility.

Table I-9. Winchester Drive Compatibility

| Compatibility                 | Vendor                                                     | Model                                                | Cylinders                              | Heads                      | Unformatted Capacity (MB)                          |

|-------------------------------|------------------------------------------------------------|------------------------------------------------------|----------------------------------------|----------------------------|----------------------------------------------------|

| Fully ST506<br>Compatible (1) | Seagate<br>TI                                              | ST506<br>ST506                                       | 153<br>153                             | 4<br>4                     | 6.38<br>6.38                                       |

| Fully ST406<br>Compatible (1) | Ampex (2)<br>CMI<br>IMI<br>Rodime (2)<br>Seagate<br>Tandon | PYXIS7<br>CM5206<br>5006<br>RC201<br>ST406<br>TM501  | 306<br>306<br>306<br>306<br>306<br>306 | 2<br>2<br>2<br>2<br>2<br>2 | 6.38<br>6.38<br>6.38<br>6.38<br>6.38<br>6.38       |

| Fully ST412<br>Compatible (1) | Ampex (2)<br>CMI<br>IMI<br>Rodime (2)<br>Seagate<br>Tandon | PYXIS13<br>CM5412<br>5012<br>R0202<br>ST412<br>TM502 | 306<br>306<br>306<br>306<br>306<br>306 | 4<br>4<br>4<br>4<br>4<br>4 | 12.76<br>12.76<br>12.76<br>12.76<br>12.76<br>12.76 |

| Fully ST419<br>Compatible (1) | Ampex (2)<br>CMI<br>IMI<br>Rodime (2)<br>Seagate<br>Tandon | PYXIS20<br>CM5619<br>5013<br>R0203<br>ST419<br>TM503 | 306<br>306<br>306<br>306<br>306<br>306 | 6<br>6<br>6<br>6<br>6<br>6 | 19.14<br>19.14<br>19.14<br>19.14<br>19.14<br>19.14 |

Table I-9. Winchester Drive Compatibility (continued)

| Compatibility | Vendor  | Model      | Cylinders | Heads | Unformatted Capacity (MB) |

|---------------|---------|------------|-----------|-------|---------------------------|

| ST406/412/419 | Ampex   | PYXIS27(4) | 320       | 8     | 26.67                     |

| Compatible    | Atasi   | 3033       | 645       | 5     | 33.59                     |

| Except        |         | 3046 (4)   | 645       | 7     | 47.03                     |

| Capacity (3)  | CMI     | C15425     | 640       | 4     | 26.00                     |

|               |         | C16640     | 640       | 6     | 40.00                     |

|               | Evotek  | ET5530(4)  | 375       | 6     | 23.00                     |

|               |         | ET5540(4)  | 375       | 8     | 31.00                     |

|               | Quantum | QS20       | 512       | 4     | 21.00                     |

|               |         | QS40       | 512       | 8     | 42.00                     |

|               | Maxtor  | XT-1065(4) | 918       | 7     | 66.94                     |

|               |         | XT-1105(4) | 918       | 11    | 105.19                    |

|               |         | XT-1140(4) | 918       | 15    | 143.44                    |

|               | Rodime  | R0204      | 320       | 8     | 26.67                     |

|               |         | R0208 (4)  | 640       | 8     | 53.33                     |

|               | Tandon  | TW703 (4)  | 600       | 5     | 31.25                     |

|               | Vertex  | V130 (4)   | 987       | 3     | 31.00                     |

|               |         | V150 (4)   | 987       | 5     | 51.67                     |

|               |         | V170 (4)   | 987       | 7     | 72.33                     |

All the fully Seagate compatible drives should have the drive straps W1-W4 defined as if they were Seagate drives.

(See Section II-C)

These drives actually have 320 cylinders. However, the FWD6006 only uses the lower 306 cylinders.

All the drives which are Seagate compatible except the capacity have their own drive strap definition for straps W1-W4 as detailed in section II-C.

The released firmware supports these drives based on the specifications in the drive OEM manuals. However, due to drive unavailability, the firmware has not been fully tested with these drives.

## II. PREPARATION FOR USE

The single board FWD8006 is a complete floppy/Winchester controller. In order to use the controller in a system, however, certain controller characteristics must be selected by the user to suit his particular system requirements and the controller must be cabled to the disk drives.

## A. UNPACKING

Examine all shipping containers for evidence of damage prior to unpacking the equipment. If any damage is found, notify an authorized representative of the shipping concern before unpacking the equipment.

No special unpacking instructions are required since the shipping containers are of a standard type and easily disassembled. All sub-assemblies are adequately protected from normal shocks incurred during shipping.

Visually inspect each assembly in the shipment for damage. Check each item against the packing list to ascertain that all items have been received.

## B. I/O ADDRESS and MEMORY WAKE-UP ADDRESS SELECTION

As described in section III-B, the programmed I/O interface between the FWD8006 and the host is via a single I/O Write address. In addition, a single Multibus memory address is used as the starting address of the sequence of memory based communication and control tables, as detailed in Section III-D. So that the controller will respond to the correct addresses as chosen by the user a series of jumpers on the FWD8006 PC board must be set. The user must first, however, determine what addresses are appropriate based on three considerations:

1. The addresses chosen must be compatible with the rest of the user's Multibus system. The programmed I/O address must be unique to the FWD8006 and the wake-up address must be the system address of memory suitable for storing the Wake-up Block.

2. Some jumpering options are determined by whether the Multibus system in which the controller is to be installed uses 8 bit or 16 bit I/O addresses. Typically, small to medium sized systems using 8 bit processor based CPU boards (such as the Intel iSBC 80/20-4, iSBC 80/24, or iSBC 80/30) use 8 bit I/O addresses while 16 bit I/O addressing is reserved for larger systems using 16 bit processors or larger.

3. The wake-up address, which is actually the Multibus memory address of the Wake-up Block (Section III-D-1), is always a multiple of either 16 or 256\*, e.g. it is possible to select a wake-up address of 00420H\*\* but not possible to select an address of 00424H. Also the wake-up address and the I/O address are closely related so consideration must be given to choosing a combination which satisfies all of the various system requirements. When 16 bit I/O addressing is to be used, the I/O address is always the wake-up address divided by 16 or 256.

Thus a wake-up address of 00440H or 004400H corresponds to an I/O address of 0044H, a wake-up address of 92CD0H or 92CD00H corresponds to an I/O address of 92CDH, etc. When 8 bit I/O addressing is to be used, the I/O address is the least significant 8 bits of the wake-up address divided by 16 or 256. Thus for 8 bit I/O addressing, a wake-up address of 00440H or 004400H corresponds to an I/O address of 44H, and a wake-up address of 18680H or 186800H corresponds to an I/O address of 68H.

\* Note: For detailed information on memory address generation by the FWD8006 refer to Section III-A.

\*\* Note: The H suffix is used throughout this manual to denote a number in hexadecimal (base 16) notation. Similarly, a B suffix is used for binary numbers. Numbers without suffixes are decimal.

Once appropriate addresses have been selected, the following two steps are used to set 8 bit or 16 bit addressing and the actual I/O address on the FWD8006. Figure II-1 may be used to locate the jumpers specified.

1. If the FWD8006 is to recognize an 8 bit I/O address, remove jumper W37 and switch the jumpers at W38 and W39 to connect A-B. If it is to recognize a 16 bit I/O address, install a jumper at W37 and switch the jumpers at W38 and W39 to connect B-C.

2. The actual I/O address bits are set by jumpers W21 thru W36 by following this procedure:

Divide the wake-up address by 16 or 256 (Section III-A) and then converted to a 16 bit binary number, right justified.

E.g.

$$\begin{aligned} 00440H / 16 &= 44H = 0000000001000100B \\ 92CD0H / 256 &= 92CDH = 1001001011001101B \end{aligned}$$

The 16 bits are copied to the table below, one bit per box.

Jumpers are INSTALLED at those W locations over 1s in the table.

Jumpers are REMOVED from those W locations over 0s in the table.

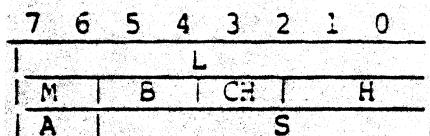

| W21 | W22 | W23 | W24 | W25 | W26 | W27 | W28 | W29 | W30 | W31 | W32 | W33 | W34 | W35 | W36 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

The FWD8006 is currently shipped from the factory with:

Wake-up address = 00040H or 000400H

I/O address = 04H

8 bit I/O recognized

This strapping is subject to change without notice.

## C. OPTION STRAPPING

In addition to the address selection described in the preceding section, the FWD8006 PC board contains additional jumper locations which are used to configure the controller to the user's particular Multibus system. They are described below and may be located on the PC board by referring to Figure II-1. The configuration as supplied by SMS is shown in parentheses with each jumper function.

## W1-W3 Define First Winchester Drive (W3-AB Installed)

Jumpers W1 through W3 are used to define the first Winchester drive according to the following table:

|               |         | <u>W1-AB</u> | <u>W1-BC</u> | <u>W2-AB</u> | <u>W2-BC</u> | <u>W3-AB</u> | <u>W3-BC</u> |

|---------------|---------|--------------|--------------|--------------|--------------|--------------|--------------|

| No Winchester |         | R            | R            | R            | R            | R            | R            |

| Seagate       | ST506   | R            | R            | R            | R            | R            | I            |

|               | ST406   | R            | R            | R            | R            | I            | R            |

|               | ST412   | R            | R            | R            | I            | R            | R            |

|               | ST419   | R            | R            | R            | I            | R            | I            |

| Rodime        | R0208   | R            | R            | R            | I            | I            | R            |

|               |         |              |              |              |              |              |              |

| Vertex        | V130    | R            | R            | I            | R            | R            | R            |

|               | V150    | R            | R            | I            | R            | R            | I            |

|               | V170    | R            | R            | I            | R            | I            | R            |

| Tandon        | T1703   | R            | I            | R            | R            | R            | R            |

| Atasi         | 3033    | R            | I            | R            | I            | R            | I            |

|               | 3046    | R            | I            | R            | I            | I            | R            |

| Maxtor        | XT-1065 | R            | I            | I            | R            | R            | R            |

|               | XT-1105 | R            | I            | I            | R            | R            | I            |

|               | XT-1140 | R            | I            | I            | R            | I            | R            |

| Rodime        | R0204   |              |              |              |              |              |              |

|               | PYXIS27 | I            | R            | R            | R            | R            | R            |

| Evotek        | ET5530  | I            | R            | R            | R            | R            | I            |

|               | ET5540  | I            | R            | R            | R            | I            | R            |

|         |         |   |   |   |   |   |   |

|---------|---------|---|---|---|---|---|---|

| CMI     | Q16426  | I | R | R | I | R | R |

|         | CM6640  | I | R | R | I | R | I |

| Quantum | Q520    | I | R | R | I | I | R |

|         | Q540    | I | R | I | R | R | R |

| CDC     | 9415-36 | I | R | I | R | R | I |

R = Removed

I = Installed

All other possible combinations are reserved.

For drive compatibility, refer to Table I-9.

#### W4 Define Second Winchester Drive (both AB, BC Removed)

Jumpers W4 is used to define the second Winchester drive as follows:

##### W4-AB W4-BC

|   |   |                                                   |

|---|---|---------------------------------------------------|

| R | R | Same as the first one defined by W1-AB thru W3-BC |

| R | I | Reserved                                          |

| I | R | Reserved                                          |

#### W5-W7 Define Floppy Drives (W7-AB Installed)

Jumpers W5 through W7 are used to define the two floppy drives according to the following table:

|           | <u>W5-AB</u> | <u>W5-BC</u> | <u>W6-AB</u> | <u>W6-BC</u> | <u>W7-AB</u> | <u>W7-BC</u> |

|-----------|--------------|--------------|--------------|--------------|--------------|--------------|

| No floppy | R            | R            | R            | R            | R            | R            |

| SA310     | R            | R            | R            | R            | R            | I            |

| SA350     | R            | R            | R            | R            | I            | R            |

| M2896-63  |              |              |              |              |              |              |

| TM848-2E  |              |              |              |              |              |              |

| TM848-1   | R            | R            | R            | I            | R            | R            |

| TM848-2   | R            | R            | R            | I            | R            | I            |

| SA850     | R            | R            | R            | I            | I            | R            |

| SA400     | R            | R            | I            | R            | R            | R            |

| SA450     | R            | R            | I            | R            | R            | I            |

| SA410     | R            | R            | I            | R            | I            | R            |

| SA460     | R            | I            | R            | R            | R            | R            |

| FD-55F    |              |              |              |              |              |              |

|         |   |   |   |   |   |   |

|---------|---|---|---|---|---|---|

| MPI91   | R | I | R | R | R | I |

| MPI92   | R | I | R | R | I | R |

| TM100-3 | R | I | R | I | R | R |

| TM100-4 | R | I | R | I | R | I |

| SA455   | R | I | R | I | I | R |

| FD-55B  |   |   |   |   |   |   |

| SA800   | R | I | I | R | R | R |

| SA465   | R | I | I | R | R | I |

| QA-D33V | R | I | I | R | I | R |

Note: The two floppy drives should be of the same type.

All other possible combinations are reserved.

#### W8 Enable Power On Reset Delay (Installed)

Installed: A 15 second power on reset delay is enabled before the controller can respond to any host command. During the 15 second delay, the on board LED will blink for approximately 7 times.

Removed: There will be no delay, i.e. as soon as power is turned on, the controller can respond to host command immediately.

#### W9 Enable Reset Self Test (Installed)

Installed: Upon detection of the second programmed I/O Start command after reset (Section III-3), a comprehensive set of internal controller diagnostics is executed. If an error is detected status is posted and an interrupt is generated.

Removed: No diagnostics are executed except via the Diagnostic Command.

#### W10 Enable 16 Bit System Bus (Installed)

Installed: The FWD8006 will assume that all memory to which it is directed supports word transfers which it will use when appropriate.

Removed: The FWD8006 will only do byte data transfers to the Multibus except for data buffers where word transfers are flagged by the appropriate Modifier bit (Section III-F-2) and then only if W11 is installed to enable the command extension.

### W11-W12 Enable Command Extension and Direct/Buffered Transfers (W11 Installed)

W11, when installed, enables all the extended mode operations except direct/buffered transfers. In extended mode, FWD8006 command forms which are not available with the Intel iSBC215/iSX218 combinations are allowed. (For detail of extended mode operation see modifier byte of IOPB block in section III.D.4.)

If W11 is removed, the extended mode is disabled and only valid iSBC215/iSX218 command forms will be accepted by the FWD8006. Note that in this iSBC215/iSX218 compatible mode, the controller will post only operation complete status, not seek complete or media change status, to the host until the "Busy" byte in CCB is cleared, i.e., until the controller finishes executing a command issued by the host. This means that in the compatible mode, the report of seek complete or media change will be delayed until after the controller finishes a command. In the extended mode the controller will post status internally queued in sequence whenever the status semaphore is cleared by the host, regardless of whether it is seek complete, media change or operation complete status. Note that to be compatible with iRMX-86, W11 has to be removed and W43-AB must be installed.

Besides enabling and disabling the command extension, W11 is also used together with W12, to define four direct/buffered transfer modes. Definitions are listed below:

#### W11 W12

|     |                                                                         |

|-----|-------------------------------------------------------------------------|

| R R | Compatible mode, both floppy and Winchester transfers buffered          |

| R I | Compatible mode, floppy direct, Winchester buffered                     |

| I R | Extended mode, floppy direct, Winchester programmable by modifier byte. |

| I I | Extended mode, both floppy and Winchester transfers direct              |

This implies that bit 6 of the IOPB modifier byte (section III.D.4) is only used to define Winchester direct/buffered transfers when W11 is installed and W12 is removed.

### W13 Enable No-Host Diagnostics (BC connected by a trace on board)

AB, BC both removed: Enables normal controller operation. Straps W8 through W12 have the control functions as described above.

AB installed: Enables stand-alone diagnostics. Straps W8 through W12 have control functions related to diagnostics and host control is overridden except for reset control. Refer to section V for details of the comprehensive diagnostic capabilities available.

BC installed: The No-Host diagnostic is enabled (low) or disabled (high) by pin 38 of Multibus P2 connector.

**Note:** The controller is shipped with a trace on the board connecting W13-BC. The trace has to be cut if pin 38 of P2 is to be used for other purposes in a specific system environment or if AB is to be installed.

!!! Warning !!!

If No-Host diagnostics is enabled (W13-BC installed) and format is enabled (W11 installed) and Winchester write protect is disabled (W14 removed), a format operation will automatically be started after power on and data on Winchester will be overwritten.

W14 Enable Winchester Write Protect (BC connected by a trace on board)

AB, BC both removed: Both Winchester drives are not write protected.

AB installed: Both Winchester drives are write protected.

BC installed: Winchester write protection is controlled by pin 20 of Multibus P2 connector. Write protected if the line is driven low, not protected otherwise.

Note: The controller is shipped with a trace on the board connecting W14-BC. The trace has to be cut if pin 20 of P2 is to be used for other purposes in a specific system environment or if AB is to be installed.

W15 Enable Write Precompensation (BC connected by a trace on board)

AB, BC both removed: Not recommended if the trace between posts B and C is cut; may enable write precomp.

AB installed: Disable write precomp.

BC installed: Enable write precomp.

Note 1): The controller is shipped with a trace on the board connecting W15-BC. The trace has to be cut if AB is to be installed.

2): Even if write precomp is enabled by strap W15, the controller will override it if the Winchester drives connected to the controller are manufactured by Vertex or Maxtor because both manufacturers recommend that precomp not be enabled for their drives.

W18-W19 Select PLL timing for 8" or 5-1/4" floppies (W18-AB, W19-AB installed)

W18-AB, W19-AB installed: Select PLL integrator time constant for 8" floppy.

W18-BC, W19-BC installed: Select PLL integrator time constant for 5-1/4" floppy.

Note: All other possible combinations are illegal.

W21-W39 are described in section II-B.

## W41 Disable 8289 ANYRQST (Installed)

Installed: ANYRQST of the 8289 bus arbiter is disabled, that is lower priority master has to acquire Multibus via CBRQ/line.

Removed: ANYRQST is enabled, that is lower priority master will be treated as higher priority master.

## W42 Enable BPRO/ (Installed)

Installed: Multibus serial priority output signal is connected to P1-16. Required for serial priority systems.

Removed: BPRO/ is disconnected from P1-16 to allow BPRN/ of the next lower priority board to be driven by external circuitry. Required for non-SMS backplanes using parallel priority.

## W43 Select CBRQ/ (BC Installed)

W43-AB installed: FWD8006 Multibus arbitration circuitry is controlled by the Multibus CBRQ/ signal, P1-29. Under these conditions, the FWD8006 will release the bus to a lower priority bus master unless CBRQ/ is asserted. Compatible with iRMX-86, W43-AB must be installed.

W43-BC installed: FWD8006 Multibus arbitration circuitry behaves as if CBRQ/ is always asserted. Bus arbitration normally occurs for every Multibus access.

## W44 Select Interrupt Level (A to D wirewrapped, INT5/)

This wirewrap jumper is used to select the particular Multibus interrupt line to be asserted whenever the FWD8006 generates an interrupt. A connection is wirewrapped between W44-A and one of the other pins as follows:

| Multibus | W44 |

|----------|-----|

| INT7/    | S   |

| INT6/    | C   |

| INT5/    | D   |

| INT4/    | E   |

| INT3/    | F   |

| INT2/    | H   |

| INT1/    | J   |

| INT0/    | K   |

W45 Enable LED Driver (Connected by a trace on board)

Installed: The LED driver which drives the on-board LED is also connected to drive P2-28 line.

Removed: Disconnect the on-board LED driver from P2-28.

Note: The controller is shipped with a trace on the board connecting W45-AB. The trace has to be cut if P2-28 is to be used for other purpose in a specific environment.

W46-W49 IEEE 796 High Order Address Lines (Connected by traces on board)

These four straps connect the FWD8006 to the four most significant IEEE 796 address lines.

W47 ADR17/ P2-56

W46 ADR16/ P2-55

W49 ADR15/ P2-58

W48 ADR14/ P2-57

Note: The controller has these four traces on board. These traces have to be cut if these four pins are to be used for other purpose.

W50 Enable LOCK/ (Removed)

Installed: The LOCK/ signal generated by the controller is connected to P1-25.

Removed: Controller generated LOCK/ signal is disconnected from P1-25.

Note 1): This strap exists only on boards of revision level C and up.

2): The Multibus specifications specify that "LOCK/" cannot be asserted longer than 12 us on the Multibus. However, when the controller asserts "LOCK/" for Winchester direct transfer, it stays asserted during the whole block transfer. Hence it will violate the Multibus timing specification if this strap is installed and Winchester direct transfer is requested. It is the user's responsibility to make sure that the installation of W50 will not cause any problem in his system.

The remainder of the straps on the pc board are used for SMS manufacturing test; and are not user options. They must be strapped as follows:

Straps Installed: W20, W40 (W20 is connected by a trace on board. No strap has to be installed unless the trace is cut)

Straps Removed: W16, W17

Figure II-1. FND8006 PCB Jumper Locations

D. DRIVE STRAPPING

All the last (second) drives on the J1,J2 or J3 cable should be terminated properly as recommended by the drive manufacturer. Tables II-5 and II-6 provide detailed information on option straps for each drive supported by the FWD8006.

Table II-5. Floppy Drive OptionsSHUGART SA400/SA450/SA410/SA460

| <u>DRIVE</u> | <u>JUMPERS</u>    |                             |

|--------------|-------------------|-----------------------------|

| DRIVE 0      | Remove MX, MS, SD | Install DS1, SS, DD, RI, DA |

| DRIVE 1      | Remove MX, MS, SD | Install DS2, SS, DD, RI, DA |

Heads will load when door is closed. Door locks when drive is selected.

MICRO PERIPHERALS INC. MPI 91/92

| <u>DRIVE</u> | <u>JUMPERS</u>            |            |

|--------------|---------------------------|------------|

| DRIVE 0      | Remove T1, T3, T4, T5, T6 | Install T7 |

| DRIVE 1      | Remove T1, T2, T4, T5, T6 | Install T7 |

Heads loads when motor comes on.

TANDON TM100-3/TM100-4

| <u>DRIVE</u> | <u>JUMPERS</u>              |  |

|--------------|-----------------------------|--|

| DRIVE 0      | Remove NDS1, NDS2, NDS3, MX |  |

| DRIVE 1      | Remove NDS0, NDS2, NDS3, MX |  |

TANDON TM848-1/TM848-2

The default stepping as shipped by Tandon must be modified as follows:

| <u>DRIVE</u> | <u>JUMPERS</u>       |                                  |

|--------------|----------------------|----------------------------------|